**RISC-Linz** Research Institute for Symbolic Computation Johannes Kepler University A-4040 Linz, Austria, Europe

## Tudor JEBELEAN

(March, 1994)

RISC-Linz Report Series No. 94-37

Editors: RISC-Linz Faculty

E.S. Blurock, B. Buchberger, C. Carlson, G. Collins, H. Hong, F. Lichtenberger, H. Mayr, P. Paule, J. Pfalzgraf, H. Rolletschek, S. Stifter, F. Winkler.

Supported by: Austrian Bundesministerium für Wissenschaft und Forschung: doctoral scholarship and project 613.523/3-27a/89 (Gröbner Bases); Austrian Forschungsförderungsfonds: project S5302-PHY (Parallel Symbolic Computation); POSSO project(Polynomial Systems Solving – ESPRIT III BRA 6846).

PhD Thesis

Copyright notice: Permission to copy is granted provided the title page is also copied.

## Systolic Multiprecision Arithmetic

Dissertation

zur Erlangung des akademischen Grades "Doktor der technischen Wissenschaften"

> Eingereicht von Dipl.-Ing. Tudor Jebelean März 1993

Erster Begutachter: Zweiter Begutachter: O. Univ.-Prof. Dr. Bruno Buchberger O. Univ.-Prof. Dr. George Collins

Angefertigt am Forschungsinstitut für Symbolisches Rechnen Technisch-Naturwissenschaftliche Fakultät Johannes Kepler Universität Linz

### Supported by:

Austrian Bundesministerium für Wissenschaft und Forschung: doctoral scholarship and project 613.523/3-27a/89 (Gröbner Bases);

Austrian Forschungsförderungsfonds: project S5302-PHY (Parallel Symbolic Computation);

POSSO project (Polynomial Systems Solving – ESPRIT III BRA 6846);

#### Eidesstattliche Erklärung

Ich versichere, daß ich die Dissertation selbständing verfaßt habe, andere als die angegebenen Quellen und Hilfsmittel nicht verwendet und mich auch sonst keiner unerlaubten Hilfe bedient habe.

Tudor Jebelean Linz, September 20, 1994

#### Abstract

We study systolic algorithms for performing long integer and long rational arithmetic in computer algebra systems. Novel algorithms for *exact division* and *GCD computation* are introduced, which work *least-significant digits first*, thus being suitable for aggregation with other least-significant digits first algorithms for multiplication and addition in an integrated unit for operation with rational numbers. Experiments on **Maspar** (SIMD architecture) and **hardware** implementations using Field Programmable Logic show that a significant speed-up can be achieved.

#### Abstract

Wir studieren systolische Algorithmen für Berechnungen mit großen ganzen Zahlen (long integer arithmetic) und rationalen Zahlen innerhalb Computer Algebra systemen. Es werden neue Algorithmen für **exakte Division** und **Berechnung des größten gemeinsamen Teilers** entwickelt, welche nach dem Prinzip leastsignificant digits first arbeiten. Diese können dann mit anderen least-significant digits first Algorithmen für Multiplikation und Addition kombiniert werden, innerhalb einer integrierten Einheit zwecks Manipulationen rationaler Zahlen. Durch Experimente auf Maspar (SIMD architektur) und Hardware Impelmentierung (Field Programmable Logic) prüfen wir daß eine signifikante Performance-steierung erzielt werden kann.

# Contents

| 1 | Intr | oduction                                 | 9  |

|---|------|------------------------------------------|----|

|   | 1.1  | Prologue                                 | 10 |

|   | 1.2  | Object of the thesis                     | 15 |

|   | 1.3  | Overview                                 | 19 |

|   | 1.4  | Acknowledgments                          | 23 |

| 2 | Mot  | ivating experiments                      | 25 |

|   | 2.1  | Introduction                             | 26 |

|   | 2.2  | Timing Techniques                        | 27 |

|   |      | 2.2.1 System clock                       | 28 |

|   |      | 2.2.2 Repeated call                      | 29 |

|   |      | 2.2.3 Book-keeping                       | 29 |

|   |      | 2.2.4 Run-time tracing                   | 29 |

|   | 2.3  | Results                                  | 31 |

|   |      | 2.3.1 Long integer multiplication        | 31 |

|   |      | 2.3.2 Algorithms on integral polynomials | 31 |

|   |      | 2.3.3 Gröbner bases computation          | 35 |

|   | 2.4  | Conclusions                              | 42 |

| 3 | Surv | vey                                      | 43 |

|   | 3.1  | Goal of the survey                       | 44 |

|   | 3.2  | Non-standard arithmetic systems          | 44 |

|   | 3.3  | Cellular automata                        | 47 |

|   | 3.4  | Systolic arrays                          | 48 |

|   | 3.5  | Addition                                 | 50 |

|   | 3.6  | Multiplication                           | 50 |

|   | 3.7  | Division                                 | 55 |

|   | 3.8  | Greatest Common Divisor                  | 57 |

|   | $3.9 \\ 3.10$ | Systolic Devices60Conclusions62                                                                                                 |

|---|---------------|---------------------------------------------------------------------------------------------------------------------------------|

|   | 0.10          |                                                                                                                                 |

| 4 | Exa           | ct division 65                                                                                                                  |

|   | 4.1           | Introduction                                                                                                                    |

|   | 4.2           | The new algorithm                                                                                                               |

|   | 4.3           | GCD computation $\ldots \ldots 72$                 |

|   | 4.4           | Division modulo $2^n$                                                                                                           |

|   |               | 4.4.1 Recursive modular inversion                                                                                               |

| 5 | Syst          | olic exact division 81                                                                                                          |

|   | 5.1           | $Introduction \ldots \\ 82$                               |

|   | 5.2           | Exact division of polynomials                                                                                                   |

|   |               | 5.2.1 Sequential algorithm                                                                                                      |

|   |               | 5.2.2 Systolic algorithm: Version $0 \ldots \ldots \ldots \ldots \ldots 84$                                                     |

|   |               | 5.2.3 Systolic algorithm: Version 1                                                                                             |

|   |               | 5.2.4 Systolic algorithm: Version $2 \dots \dots \dots \dots \dots \dots \dots 90$                                              |

|   |               | 5.2.5 Systolic algorithm: Version 3 90                                                                                          |

|   | 5.3           | Exact division of long integers                                                                                                 |

|   |               | 5.3.1 Sequential algorithm $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 96$                                                |

|   |               | 5.3.2 Systolic algorithm: Version 0 $\ldots \ldots \ldots \ldots \ldots $ 97                                                    |

|   |               | 5.3.3 Systolic algorithm: Version 1 $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 102$                               |

|   |               | 5.3.4 Systolic algorithm: Version 2                                                                                             |

|   |               | 5.3.5 Systolic algorithm: Version 3 106                                                                                         |

|   | 5.4           | Conclusions                                                                                                                     |

| 6 | Gen           | eralized binary GCD 113                                                                                                         |

|   | 6.1           | Introduction                                                                                                                    |

|   | 6.2           | Modular Conjugates                                                                                                              |

|   | 6.3           | The new algorithm                                                                                                               |

|   | 6.4           | Practical experiments                                                                                                           |

|   | 6.5           | Systolic computation                                                                                                            |

| 7 | Imp           | roving multiprecision GCD 123                                                                                                   |

|   | 7.1           | The multiprecision Euclidean algorithm 124                                                                                      |

|   | 7.2           | The double digit algorithm                                                                                                      |

|   | 7.3           | On the condition $\ldots \ldots 128$ |

|   |               | 7.3.1 An exact condition                                                                                                        |

|   |               | 7.3.2 An approximative condition                                                                                                |

2

### CONTENTS

|    | 7.4                | Approximative GCD computation                                                                              | 3 |

|----|--------------------|------------------------------------------------------------------------------------------------------------|---|

|    | 7.5                | Conclusions                                                                                                | 6 |

| 8  | Con                | nparing GCD algorithms 13                                                                                  | h |

| 0  | 8.1                | Introduction                                                                                               |   |

|    | 8.2                | Description of the algorithms                                                                              |   |

|    | 0.2                | 8.2.1 Euclid                                                                                               |   |

|    |                    | 8.2.2 I-Euclid                                                                                             |   |

|    |                    | 8.2.3 I-Euclid                                                                                             |   |

|    |                    | 8.2.4 Binary and PlusMinus                                                                                 |   |

|    |                    | 8.2.5 G-Binary                                                                                             |   |

|    | 8.3                | Experiment settings and results                                                                            |   |

| 0  | <b>37</b> 71.5     | ich architecture? 14'                                                                                      | - |

| 9  | <b>vv n</b><br>9.1 | ich architecture? 14'<br>Overview of the investigation                                                     |   |

|    | 9.1<br>9.2         | Evaluation details                                                                                         |   |

|    | 9.2                |                                                                                                            |   |

|    |                    | 9.2.1         Sequent Symmetry         14           9.2.2         Impuls Multi-Transputer(T800)         14 |   |

|    |                    | 9.2.3 MasPar MP-1                                                                                          |   |

|    |                    | 9.2.4 iWarp $\dots$ 15                                                                                     |   |

|    |                    | 9.2.5 CAM-PC                                                                                               |   |

|    |                    | 9.2.6 CAL1024                                                                                              |   |

|    |                    | 9.2.7 CLi6000                                                                                              |   |

|    | 9.3                | Conclusions                                                                                                |   |

|    | 9.4                | Sources of information on the hardware                                                                     |   |

|    | 9.4                |                                                                                                            | 1 |

| 10 | •                  | tolic multiplication on MasPar 16                                                                          |   |

|    |                    | Introduction                                                                                               |   |

|    | 10.2               | Sequential classical multiplication                                                                        |   |

|    |                    | 10.2.1 Integers                                                                                            |   |

|    |                    | 10.2.2 Polynomials                                                                                         | 4 |

|    | 10.3               | Systolic algorithms                                                                                        |   |

|    |                    | 10.3.1 The MasPar computer                                                                                 |   |

|    |                    | 10.3.2 Integers                                                                                            |   |

|    |                    | 10.3.3 Polynomials                                                                                         | 2 |

| 11 | Rat                | ional arithmetic on MasPar 179                                                                             | • |

|    | 11.1               | Introduction                                                                                               | 0 |

|    | 11.2               | Multiplication and addition                                                                                | 1 |

|    | 11.3                                                               | Greatest Common Divisor                                                                                                                                                                                                                           | 183                                                       |

|----|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|

|    | 11.4                                                               | Exact division                                                                                                                                                                                                                                    | 186                                                       |

|    | 11.5                                                               | Experimental results                                                                                                                                                                                                                              | 187                                                       |

| 12 | Har                                                                | dware implementation 1                                                                                                                                                                                                                            | 89                                                        |

|    | 12.1                                                               | Introduction                                                                                                                                                                                                                                      | 90                                                        |

|    | 12.2                                                               | Rational addition                                                                                                                                                                                                                                 | 92                                                        |

|    | 12.3                                                               | Multiplication                                                                                                                                                                                                                                    | 193                                                       |

|    |                                                                    | Addition                                                                                                                                                                                                                                          |                                                           |

|    |                                                                    | Systolic GCD computation 1                                                                                                                                                                                                                        |                                                           |

|    |                                                                    | Adapting systolic PlusMinus algorithm                                                                                                                                                                                                             |                                                           |

|    |                                                                    | Exact division                                                                                                                                                                                                                                    |                                                           |

|    |                                                                    | Experiments and conclusions                                                                                                                                                                                                                       |                                                           |

|    |                                                                    |                                                                                                                                                                                                                                                   |                                                           |

| 13 | Con                                                                | clusions 2                                                                                                                                                                                                                                        | 13                                                        |

|    |                                                                    |                                                                                                                                                                                                                                                   | 13 $31$                                                   |

| A  | Res                                                                | earch papers related to the thesis 2                                                                                                                                                                                                              |                                                           |

| A  | Res                                                                | earch papers related to the thesis 2                                                                                                                                                                                                              | 31<br>33                                                  |

| A  | Res<br>Cur                                                         | earch papers related to the thesis 2<br>riculum Vitae 2                                                                                                                                                                                           | <b>31</b><br><b>33</b><br>233                             |

| A  | Reso<br>Cur<br>B.1                                                 | earch papers related to the thesis2riculum Vitae2Personal Data2Education2                                                                                                                                                                         | <b>31</b><br>33<br>233<br>233                             |

| A  | Reso<br>Cur<br>B.1<br>B.2                                          | earch papers related to the thesis2riculum Vitae2Personal Data2Education2Professional Experience2                                                                                                                                                 | <b>31</b><br><b>33</b><br>233<br>233<br>234               |

| A  | <b>Res</b><br><b>Cur</b><br>B.1<br>B.2<br>B.3                      | earch papers related to the thesis       2         riculum Vitae       2         Personal Data       2         Education       2         Professional Experience       2         Lecturing Experience       2                                     | <b>31</b><br>33<br>233<br>233<br>234<br>234               |

| A  | <b>Res</b><br><b>Cur</b><br>B.1<br>B.2<br>B.3<br>B.4               | earch papers related to the thesis2riculum Vitae2Personal Data2Education2Professional Experience2                                                                                                                                                 | <b>31</b><br>233<br>233<br>234<br>234<br>234<br>235       |

| A  | <b>Res</b><br><b>Cur</b><br>B.1<br>B.2<br>B.3<br>B.4<br>B.5        | earch papers related to the thesis       2         riculum Vitae       2         Personal Data       2         Education       2         Professional Experience       2         Lecturing Experience       2         Refereeing activity       2 | <b>31</b><br>33<br>233<br>234<br>234<br>234<br>235<br>235 |

| A  | <b>Res</b><br><b>Cur</b><br>B.1<br>B.2<br>B.3<br>B.4<br>B.5<br>B.6 | earch papers related to the thesis2riculum Vitae2Personal Data2Education2Professional Experience2Lecturing Experience2Refereeing activity2Systems Experience2                                                                                     | <b>31</b><br>33<br>233<br>234<br>234<br>235<br>235<br>235 |

4

# List of Figures

| 1.1  | A systolic system                                            | 16 |

|------|--------------------------------------------------------------|----|

| 1.2  | Research plan                                                | 17 |

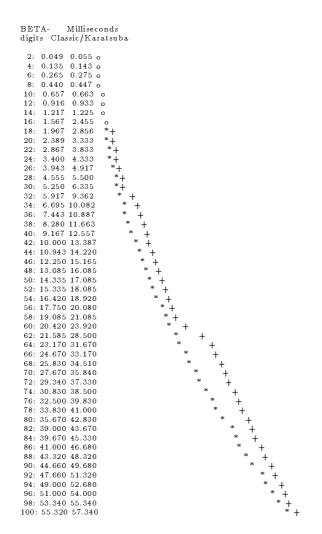

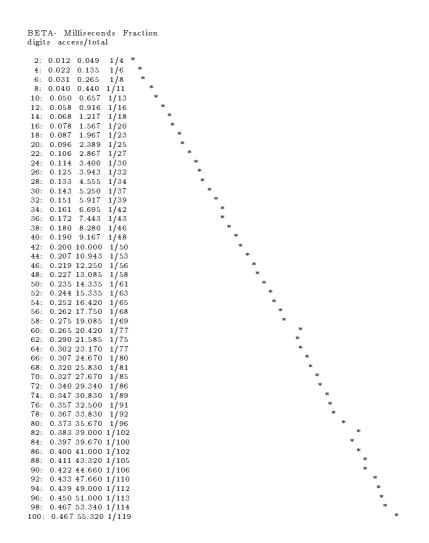

| 2.1  | Multiplication time for classic and Karatsuba algorithm      | 30 |

| 2.2  | Fraction of time consumed for accessing the operands and the |    |

|      | result in long integer multiplication.                       | 32 |

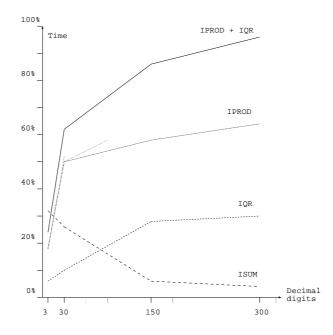

| 2.3  | Integer arithmetic within IPFAC (plot)                       | 33 |

| 2.4  | Integer arithmetic within IPSPRS (plot)                      | 34 |

| 2.5  | Integer arithmetic within IPFAC (table)                      | 35 |

| 2.6  | Integer arithmetic within IPSPRS (table)                     | 36 |

| 2.7  | Integer arithmetic within IPRES (table)                      | 36 |

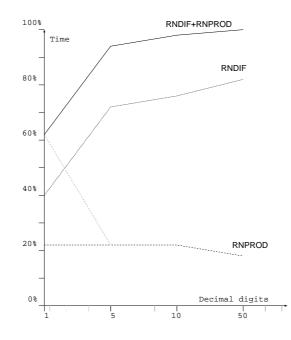

| 2.8  | Rational arithmetic within Gröbner Bases (plot)              | 38 |

| 2.9  | Rational arithmetic within Gröbner Bases (table).            | 38 |

| 2.10 | Integer arithmetic within Gröbner Bases (plot)               | 39 |

| 2.11 | Integer arithmetic within Gröbner Bases (table).             | 39 |

| 2.12 | Comparative trace analysis of Gröbner Bases for 1 vs 5 deci- |    |

|      | mal digits                                                   | 41 |

| 3.1  | A cellular automaton.                                        | 47 |

| 3.2  | A systolic system suited for variable size problems          | 49 |

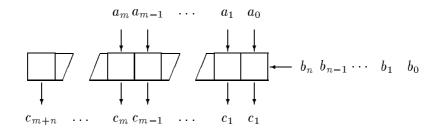

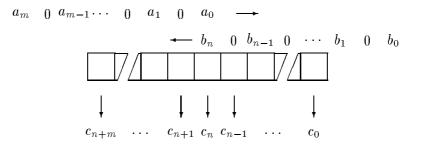

| 3.3  | Serial-parallel multiplication.                              | 53 |

| 3.4  | Multiplication with contraflowing operands                   | 54 |

| 3.5  | Atrubin multiplication algorithm.                            | 55 |

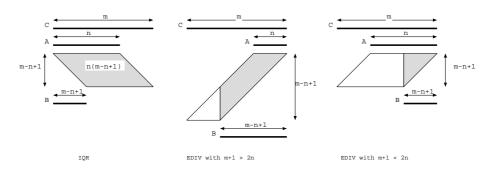

| 4.1  | EDIV: the algorithm for exact division.                      | 68 |

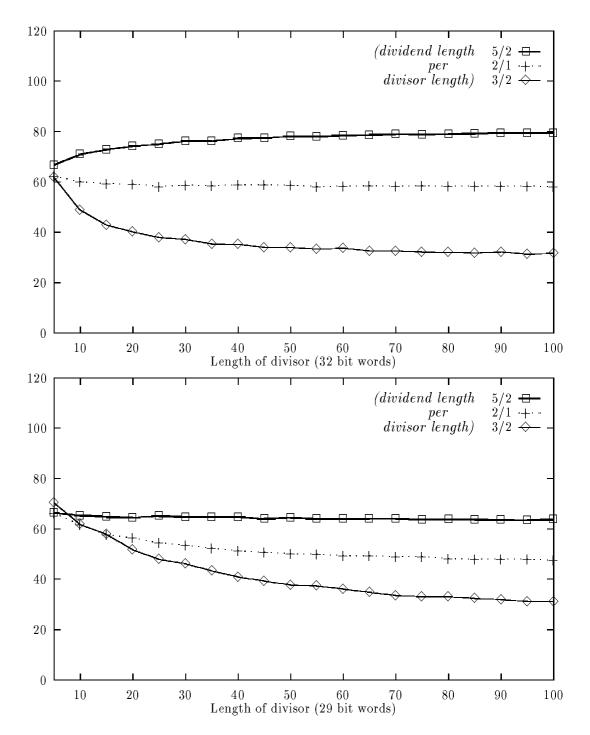

| 4.2  | Evaluation of computing times                                | 71 |

| 4.3  | EDIV/IQR % comparative timings, under GNU (top) and          |    |

|      | SACLIB (bottom).                                             | 73 |

| 4.4  | EDGCD: Exact division based GCD algorithm.                   | 74 |

| 4.5   | Benchmarks of EDGCD and modified Euclidean GCD 76                      |

|-------|------------------------------------------------------------------------|

| 4.6   | MODIV: the algorithm for modular division                              |

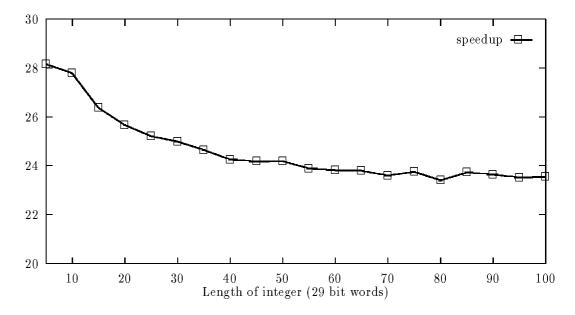

| 4.7   | Speed up of modular inverse using SACLIB                               |

| 4.8   | MODIV2: binary algorithm for division modulo $2^n$                     |

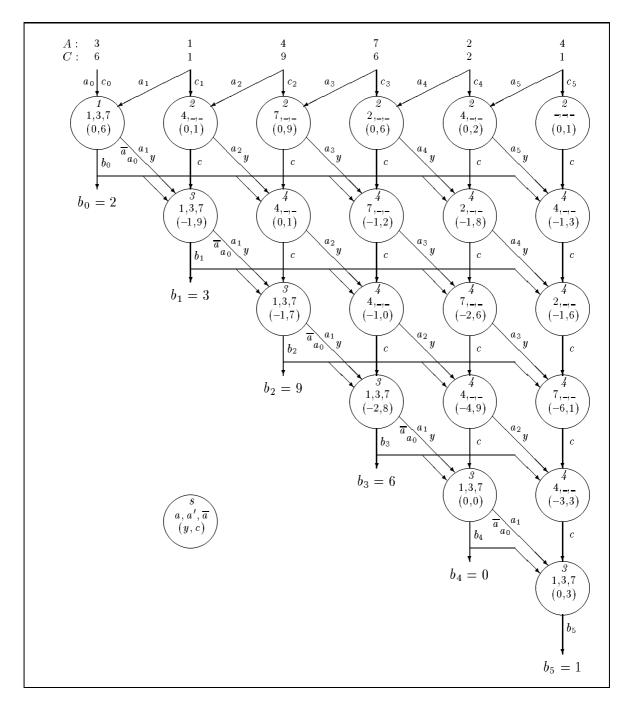

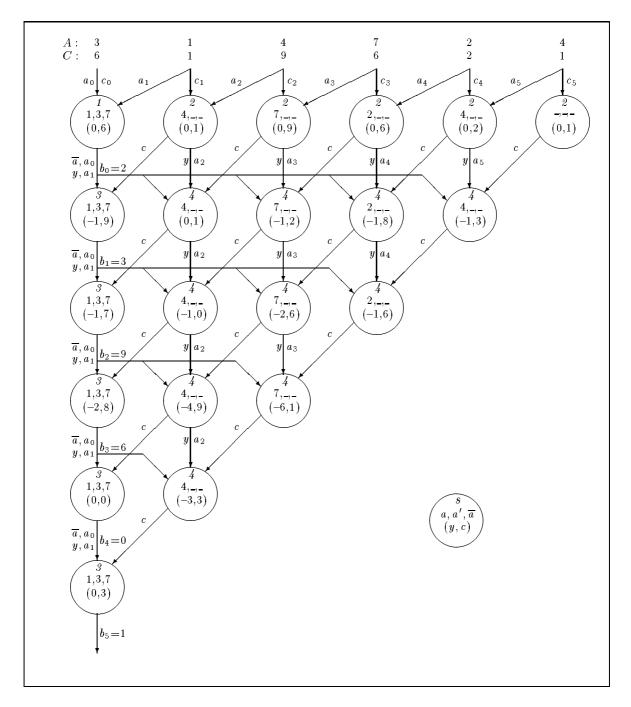

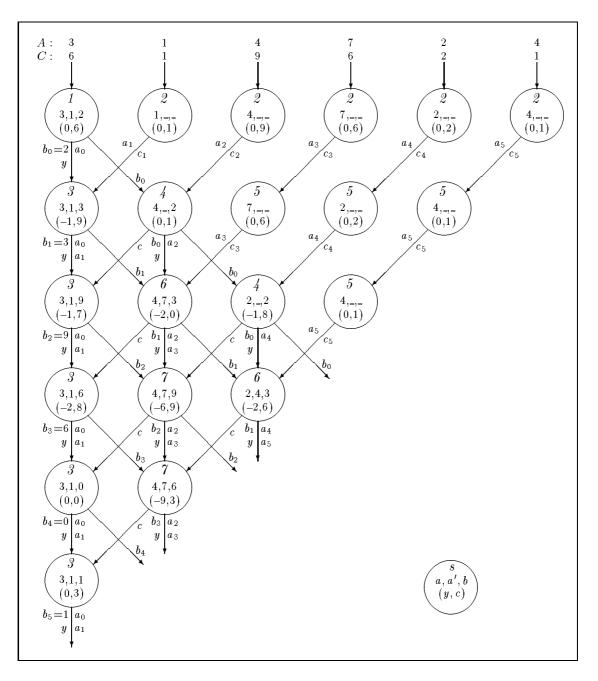

| 5.1   | Sequential algorithm for polynomial exact division                     |

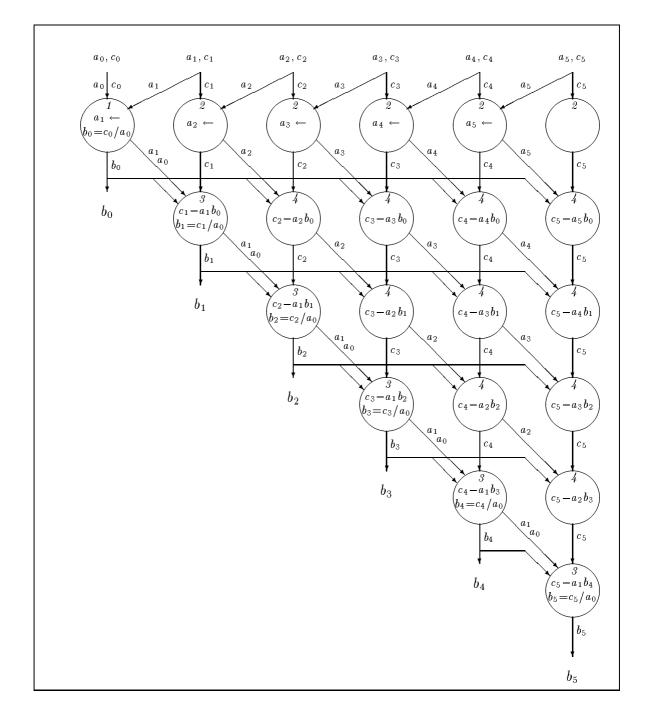

| 5.2   | Data flow in version 0 of systolic polynomial exact division 86        |

| 5.2   | Systolic algorithm for polynomial exact division: version 0 87         |

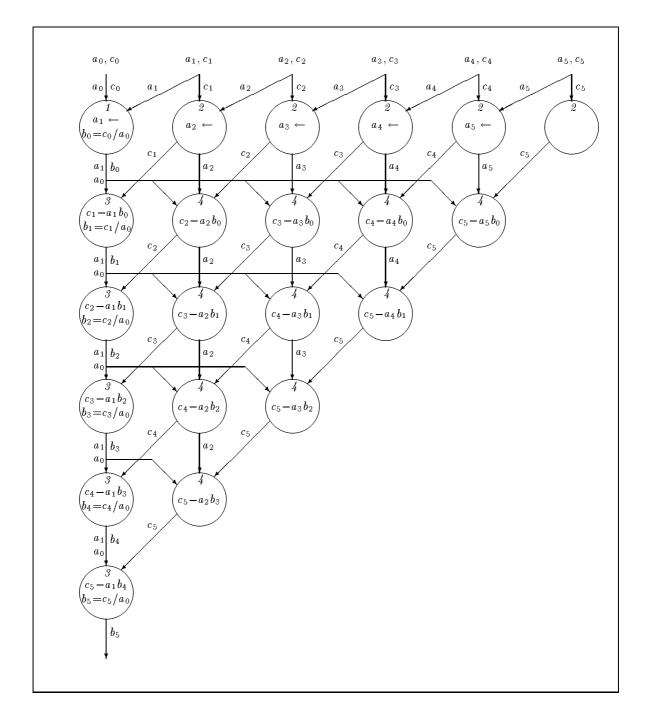

| 5.4   | Data flow in version 1 of systolic polynomial exact division 88        |

| 5.5   | Version 1 of the algorithm for polynomial exact division 89            |

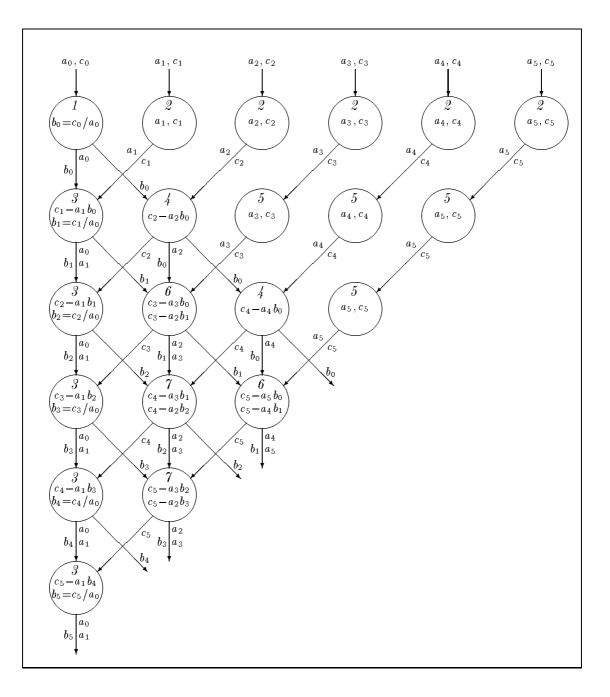

| 5.6   | Data flow in version 2 of systolic polynomial exact division. 91       |

| 5.7   | Version 2 of the algorithm for polynomial exact division 92            |

| 5.8   | Data flow in version 3 of systolic polynomial exact division. 93       |

| 5.9   | Version 3 of the algorithm for polynomial exact division 95            |

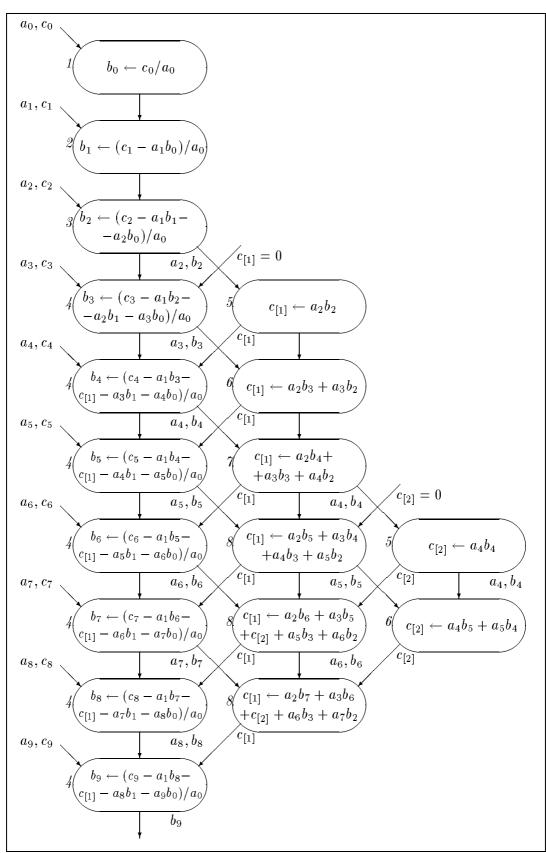

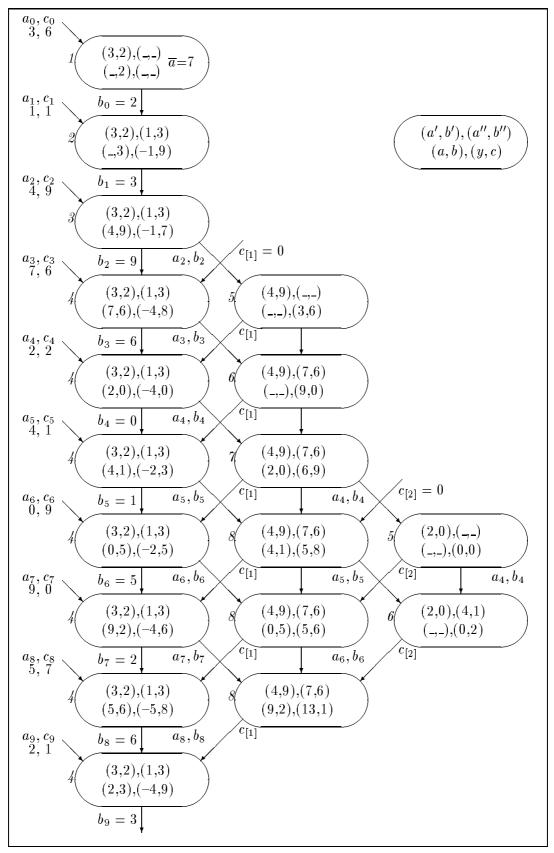

| 5.10  | Sequential algorithm for long integer exact division 98                |

| 5.11  | Parallel algorithm for long integer exact division                     |

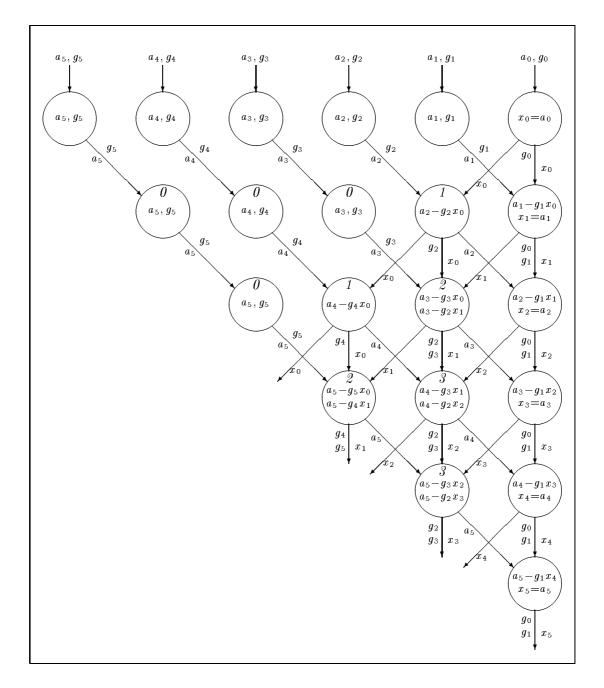

|       | Systolic algorithm for exact division of long integers: version 0.100  |

|       | Data flow in version 0 of systolic exact division of long integers.101 |

|       | Data flow in version 1 of systolic exact division of long integers.103 |

|       | Version 1 of the algorithm for exact division of integers 104          |

|       | Data flow in version 2 of systolic exact division of integers 105      |

|       | Version 2 of the algorithm for exact division of integers 107          |

|       | Data flow in version 3 of systolic exact division of long integers.108 |

|       | Version 3 of the algorithm for exact division of long integers. 110    |

| 7.1   | Benchmarks of GCD computation using single digit DPCC                  |

| 1.1   | (columns S) vs. double digit DPCC2 (columns D) 127                     |

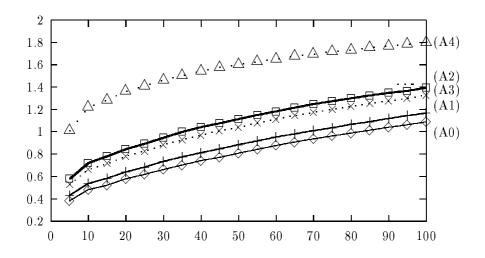

| 7.2   | Speed-up for successive improvements of version A (length of           |

|       | inputs from 5 to 100 32-bit words)                                     |

| 7.3   | Experiments with multiprecision GCD algorithm using "ex-               |

| • • • | act" condition (columns E) vs. Collins' condition (columns             |

|       | C)                                                                     |

| 7.4   | Benchmarks of version B (improved condition in DPCC): "ex-             |

|       | act" condition (columns B0) vs. "combined" condition (co-              |

|       | lumns B1).                                                             |

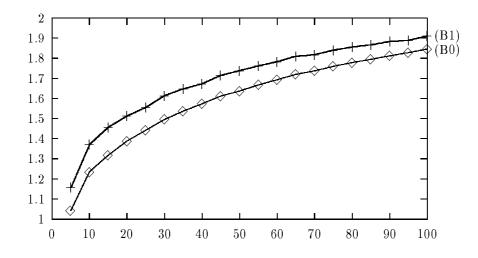

| 7.5   | Speed-up for successive improvements of version B (length of           |

|       | inputs from 5 to 100 32-bit words)                                     |

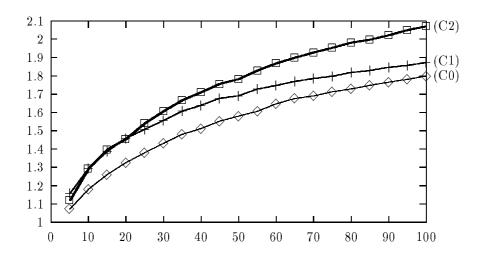

| 7.6   | Speed-up for successive improvements of version C (length of           |

|       | inputs from 5 to 100 32-bit words)                                     |

## LIST OF FIGURES

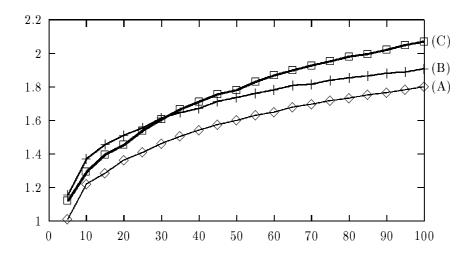

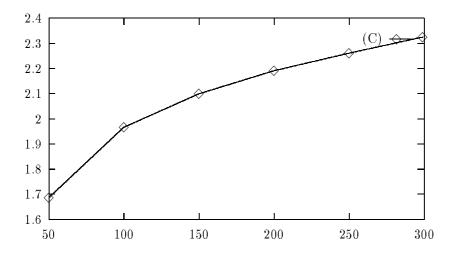

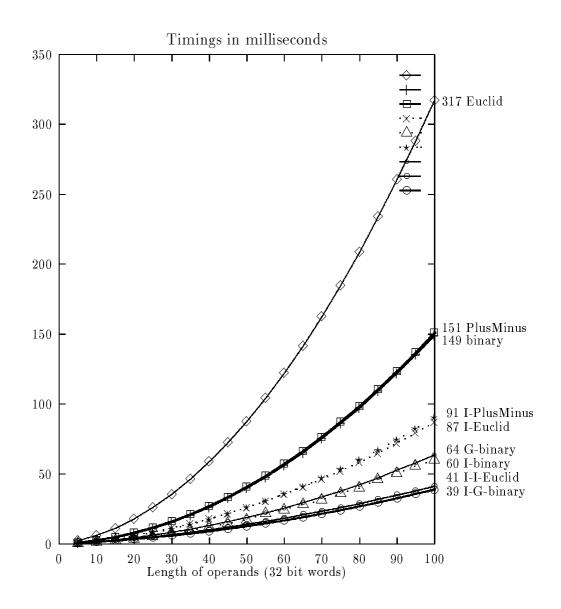

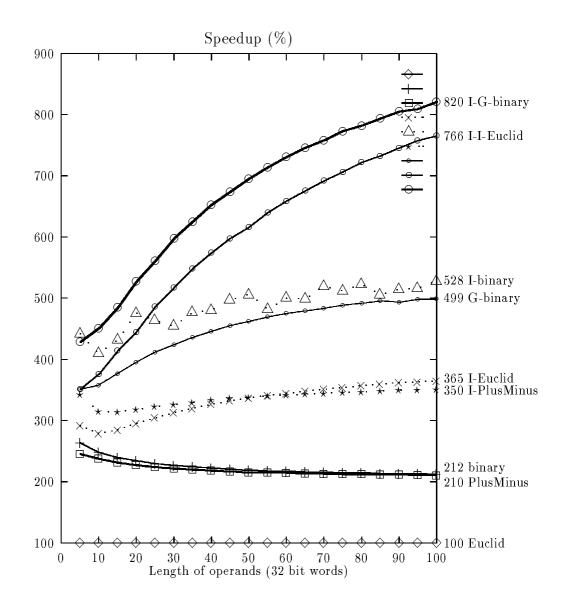

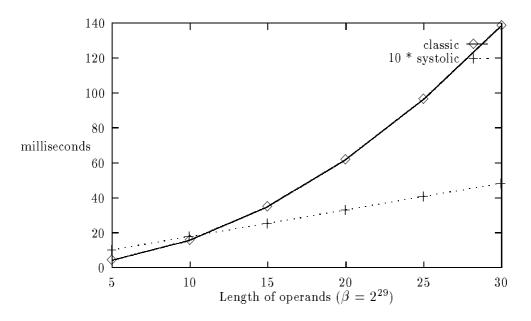

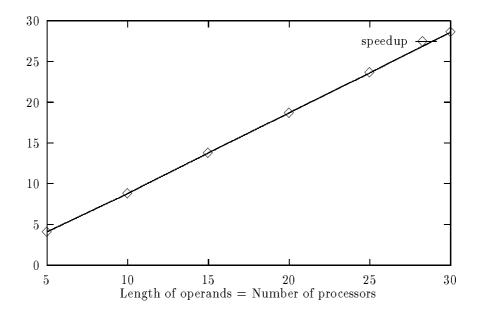

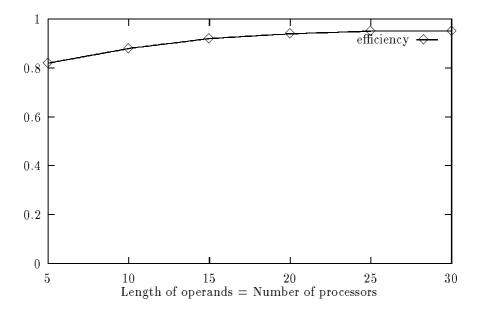

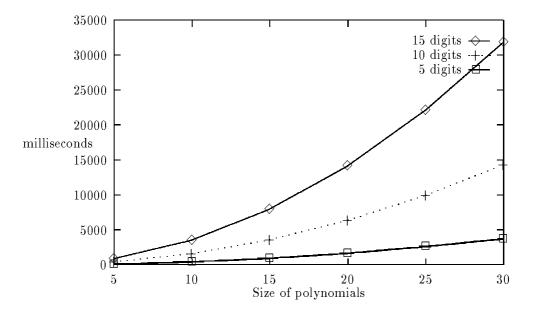

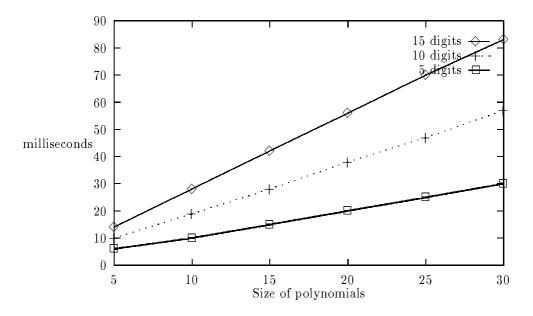

| 8.1       Comparison of absolute timings.       137         8.2       Speed-up over the Euclidean algorithm.       145         8.2       Speed-up over the Euclidean algorithm.       146         9.1       Summary of technical data       150         10.1       Classical multiplication multiplication       164         10.2       Classical multiplication of polynomials       165         10.3       A sample MasPar program       166         10.4       Parallel integer multiplication       168         10.5       Systolic multiprecision multiplication, version 1.       169         10.6       Comparative timings for multiprecision multiplication.       170         10.7       Speed-up of systolic multiprecision multiplication.       171         10.8       Efficiency of systolic multiprecision multiplication.       171         10.9       Systolic multiprecision multiplication.       172         10.10Systolic polynomial multiplication.       173         10.11Timings of classical polynomial multiplication.       175         10.13Speed-up of systolic polynomial multiplication.       175         10.14Efficiency of systolic polynomial multiplication.       175         10.14Efficiency of systolic polynomial multiplication.       185         11.1       Syst | 7.7 $7.8$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Speed-up for version (C) on very long inputs (50 to 300 words                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 137                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

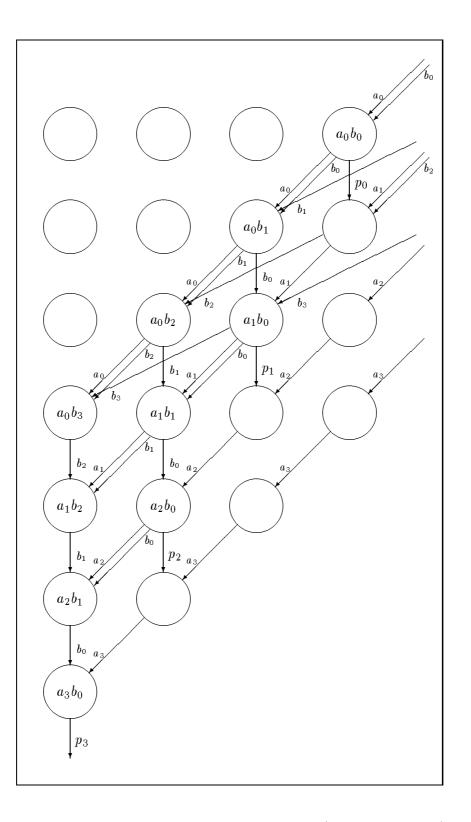

| 10.1Classical multiplecision multiplication16410.2Classical multiplication of polynomials16510.3A sample MasPar program16610.4Parallel integer multiplication16810.5Systolic multiprecision multiplication, version 1.16910.6Comparative timings for multiprecision multiplication.17010.7Speed-up of systolic multiprecision multiplication.17110.8Efficiency of systolic multiprecision multiplication.17110.9Systolic multiprecision multiplication, version 2.17210.10Systolic polynomial multiplication.17310.11Timings of classical polynomial multiplication.17510.13Speed-up of systolic polynomial multiplication.17510.14Efficiency of systolic polynomial multiplication.17611.1Systolic multiprecision addition.18211.2Systolic multiprecision addition.18211.3Systolic multiprecision exact division.18711.4Timings of the rational reduction and its components.18812.1Structure of rational adder.19412.2Structure of ne systolic cell for multiplication.19712.4Implementing two multiplication steps in one cycle.19812.5Processing element of the addition unit.19812.6Structure of one systolic cell for GCD computation.202                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Comparison of absolute timings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                           |

| 10.2Classical multiplication of polynomials16510.3A sample MasPar program16610.4Parallel integer multiplication16810.5Systolic multiprecision multiplication, version 1.16910.6Comparative timings for multiprecision multiplication.17010.7Speed-up of systolic multiprecision multiplication.17110.8Efficiency of systolic multiprecision multiplication.17110.9Systolic multiprecision multiplication, version 2.17210.10Systolic polynomial multiplication.17310.11Timings of classical polynomial multiplication.17510.13Speed-up of systolic polynomial multiplication.17510.13Speed-up of systolic polynomial multiplication.17611.1Systolic multiprecision addition.18211.2Systolic multiprecision addition.18212.3Systolic multiprecision exact division.18711.4Timings of the rational reduction and its components.19412.2Structure of rational adder.19412.3Data flow in systolic cell for multiplication.19712.4Implementing two multiplication steps in one cycle.19812.5Processing element of the addition unit.19812.6Structure of one systolic cell for GCD computation.202                                                                                                                                                                                                                | 9.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Summary of technical data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 150                                                                       |

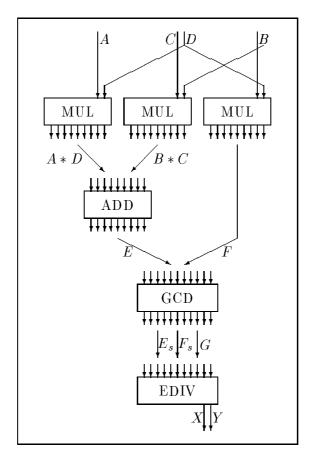

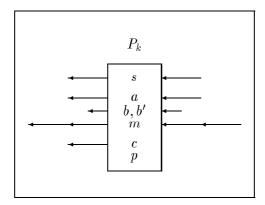

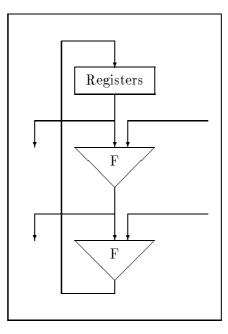

| 11.1Systolic multiprecision addition.18211.2Systolic multiprecision GCD computation.18511.3Systolic multiprecision exact division.18711.4Timings of the rational reduction and its components.18812.1Structure of rational adder.19412.2Structure of one systolic cell for multiplication.19512.3Data flow in systolic multiplication (carries not shown).19712.4Implementing two multiplication steps in one cycle.19812.5Processing element of the addition unit.19812.6Structure of one systolic cell for GCD computation.202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $10.2 \\ 10.3 \\ 10.4 \\ 10.5 \\ 10.6 \\ 10.7 \\ 10.8 \\ 10.9 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ 10.1 \\ $ | Classical multiplication of polynomialsA sample MasPar programParallel integer multiplicationSystolic multiprecision multiplication, version 1.Comparative timings for multiplication, version 1.Speed-up of systolic multiprecision multiplication.Efficiency of systolic multiprecision multiplication.Systolic multiprecision multiplication.Systolic multiprecision multiplication.Systolic multiprecision multiplication.Systolic multiprecision multiplication.Systolic polynomial multiplication.Timings of classical polynomial multiplication.Speed-up of systolic polynomial multiplication.Speed-up of systolic polynomial multiplication. | 165<br>166<br>168<br>169<br>170<br>171<br>171<br>172<br>173<br>174<br>175 |

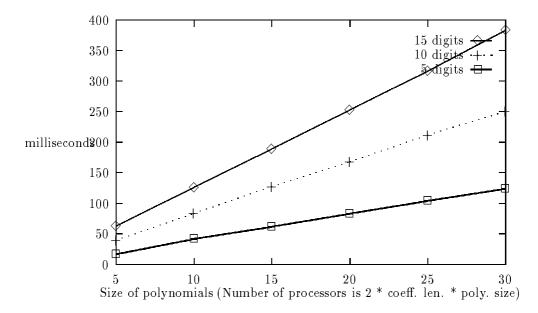

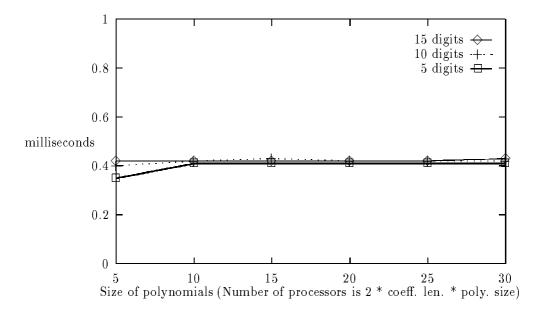

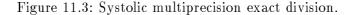

| <ul> <li>12.2 Structure of one systolic cell for multiplication</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11.1<br>11.2<br>11.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Systolic multiprecision addition.Systolic multiprecision GCD computation.Systolic multiprecision exact division.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $182 \\ 185 \\ 187$                                                       |

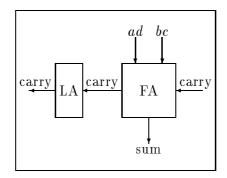

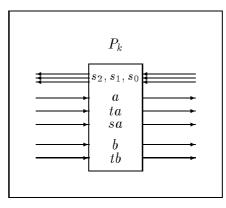

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $12.2 \\ 12.3 \\ 12.4 \\ 12.5 \\ 12.6$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Structure of one systolic cell for multiplication.Data flow in systolic multiplication (carries not shown).Implementing two multiplication steps in one cycle.Processing element of the addition unit.Structure of one systolic cell for GCD computation.                                                                                                                                                                                                                                                                                                                                                                                             | 195<br>197<br>198<br>198<br>202                                           |

LIST OF FIGURES

## Chapter 1

## Introduction

The lack of *efficiency* of the classical so called "von Neumann" architecture is due to the low use of hardware in todays computers. The *systolic paradigm* promises a spectacular improvement.

However, designing systolic algorithms seems much more difficult than designing "classical" algorithms. We approach in this thesis the systolic design of a particular class of algorithms, which are needed in algebraic computations. These are the algorithms for computations with *long integers*, which are then aggregated in order to obtain algorithms for *long rationals*.

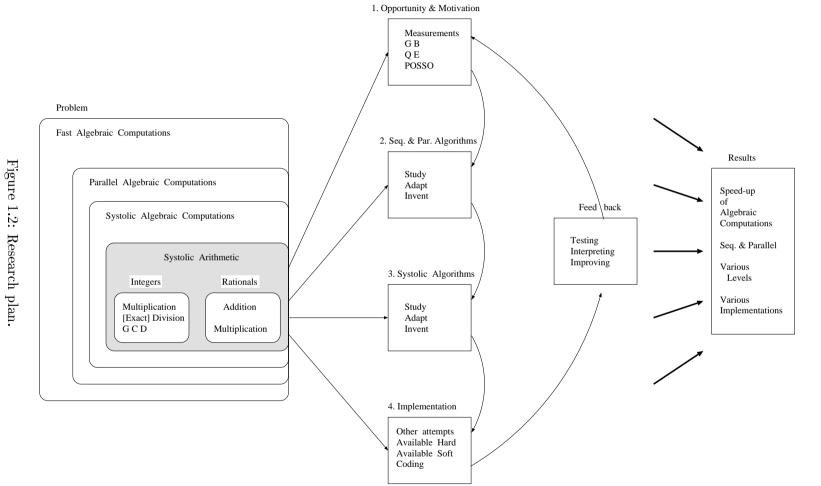

The research started with the study of sequential and parallel algorithms, then proceeded to modify, adapt and sometimes create new algorithms, and finally went all the way down to the implementation details.

All this work would not have been possible without the constant help and encouragement from my advisors and my colleagues, and without the wonderful research environment which the institute RISC is.

#### 1.1 Prologue

#### Dear reader,

The next section will open the *scientific* part of this thesis, which according to some immutable rules must be quite formal and strict, leaving very little room, if at all, for speculations and day-dreaming.

Before entering this part, please allow me to express some personal opinions which can be hardly sustained by solid facts and accurate scientific results, being rather based on approximative knowledge and vague feelings. These opinions, however, still have their roots in the present reality, and, most importantly, it is these opinions and feelings which provided me with the deep motivation for carrying out the research in this thesis.

Namely, I would like to talk about computers. Today's computers and tomorrow's computers. And when I am saying tomorrow's computers I am not thinking of Pentium or Sixtium, Alpha-chip or Beta, not even Paragon or its similar successors, nor some super-hyper-vector-Cray-like machine which might be currently sitting on the design table of the engineers. All these are, and will be, excellent machines, but they are still "today's" computers, because they are built on the same principles of today.

#### Which are wrong.

They might have been right decades ago when first computers were built, but the evolution of hardware technology made them obsolete.

In order to see this, let us compare the *computer* with another "computing" device, which is, in fact, the best we know. Let us compare it to the human *brain*:

Size: The brain has about 10<sup>10</sup> neurons, and if I am not too mistaken much by equating a neuron with the amount of circuitry needed to realize one byte of RAM, then we get 10 GigaBytes, which is quite in the range of present technology (just think what amount of hardware is in a Connection Machine 5 with 64,000 processors, each with several MegaBytes of memory).

So here we are roughly even.

**Speed:** The nervous signals travel in our body with a speed of about 10 m/s (Compare this with the light-speed of electricity!). The switching speed of a neuron is somewhere between 1/1000 and 1/100 of a second (Compare this with hundreds of MegaHertz in present circuit technology!).

#### 1.1. PROLOGUE

Hence, not only are computers faster, but they are by the orders of millions faster than the brain.

**Performance:** Yesterday when walking on the street you suddenly met a friend. It took you between 1/10 and 1/4 of a second to recognize him. Now ask your computer to do this.

Or ask the most powerful computer you know, with the best programs there are, to look at two 2D images as your eyes give to your brain, to reconstruct the 3D scene, to realize it is a street, to differentiate houses from cars and cars from trees and trees from people, to pick out faces from this scene and to differentiate them, to select a particular face from the crowd, and to finally come up with the idea:

"Hey, this is John! He looks like he's got a parking ticket."

I will not try to argue here about tasks which are better suited for computers as opposed to those which are better suited for brains. For one thing, brains are stubbornly opposed to being *programmed*, which makes it difficult to test their behavior for various tasks. My point is that the *brain* can clearly solve the tasks for which it is *already programmed* much faster and better than what we could expect from today's computers. And with the same amount of "hardware". This means that the "hardware" of the brain is used with much more

#### efficiency.

I am not saying that we should build computers to work like the human brain. I am just saying: "Yes, our computers are quite good. But there is out there another computing device which works thousands (millions?) of times more efficiently. So, aren't we having some efficiency problem with our computers? Isn't there a way to organize this hardware in such a way that it can be used more efficiently?"

Let us look at how the hardware is organized in today's computers. First there is some (small!) part of it which is called the *central processing unit* (CPU). Then there is another part of it, called *memory*, which is usually quite huge (in fact, the bigger it is, the better is the computer – we think) sitting around this CPU. Now how does this work? Well, the CPU is working all the time, while the memory, as I said, is just sitting around. OK, it is not exactly doing nothing, because, from time to time, the CPU will put or get some information into / from the memory. That is, from time to time 4 **bytes** out of those 40 millions will do something. All in all, if you think of it, at each particular moment, only a tiny part of the hardware is participating in the computation: 1/1,000 or 1/1,000,000, or less. It is like a company in which the boss is working day and night, while each of its 1,000 employees is working only when the boss is in his office.

This is not very efficient, we are not pleased with the results of this company, hence we say: "Hey, we need more employees!" (That is: add more memory). The results might improve a little, but, of course, the efficiency decreases even more!

Then we say: "Change that boss there!" (put a faster CPU). Well, similar result.

OK, this did not work, then we put a board of directors. One to bring info from the workers, one to process it, one to decide where to send the result, and one to put it there. And they will work in

#### parallel.

Rings a bell? Yes, this is the *RISC architecture*, which indeed increases the efficiency of our system, because now a larger part of the hardware is working all the time. So instead of 1/5,000 we have 1/1,000, which is a great improvement, but there is still room enough.

Which is the other architectural improvement now indispensable to any computer? It is *cache memory*, which also brings some parallelism in the use of the hardware, this time on the side of the memory. But again, just by a small amount.

So, IT'S PARALLELISM THAT WE NEED! Let us put ten such companies together, a hundred, a thousand! (That is *coarse grained parallelism*.) Now look at the results! Isn't it GREAT? Of course it is, because 10 horses pull better than one, just, this is not an automobile! The efficiency of this device cannot be higher than the efficiency of the components, and, in fact, it is even lower, because the directors of the companies must now communicate from time to time, and while they are conferring over the phone, what do their employees do? Yes, you are right, really NOTHING. Hence the efficiency decreases even further, sometimes by a large factor.

Because, indeed, we need parallelism, but *a lot of it*. The *brain* solves in **hundreds** of steps complex problems which require millions of operations because it works in parallel with thousands of tiny processors. It is like a company in which [a large part of] the employees work together. This is what we need for significantly improving the efficiency of the hardware usage in computers. Rather than having the hardware just sitting around, we should

have it *working* around, that is, it should be organized in thousands of tiny processors, working together.

Well, that's clear to many, and has been for a long time. Hardware engineers can easily build this kind of thing for us. However we want it. The only problem is: How do we want it?.

And this is THE BIG PROBLEM! For the lack of solutions to which we do not have THE efficient computers. If you have thousands of processors, each with very limited capability, how do you interconnect them? How do you organize the computation such that all (most, many) of them work together? There has been a lot of research on these things, and quite soon people found out that solving these *organizational* problems is is often much more difficult than the initial work itself. (Which is quite natural: a company in which all the people work is more difficult to organize ...) This brings us to the heart of the matter.

We need a way to organize complex computations on a very large number of small processors.

And now I can finally say that:

My thesis is not going to solve this problem.

But, at least, I am going to attack it. And because so many people attacked it top-down, frontally, in fair-fight, and failed, I will attack it bottomup, by the side, viciously at Achilles' heel. Namely, I will **not** try to find an *universally* perfect architecture and a way to efficiently map *any* algorithm on this architecture. Rather, I will consider a certain architecture,

#### the systolic one,

which is quite simple, and yet has the basic characteristics of what we are looking for, and I will try to implement efficiently on it a certain class of algorithms:

#### long integer arithmetic in symbolic computation,

which is limited, but large enough to be of practical interest.

This approach has the obvious disadvantage that it will not solve the problem (which is what is not expected from me anyway), but it also has some advantages:

• It leads to some practical algorithms / implementations which are useful for applications.

- It gives some insight into "Why things [do not] work" with this model, which is a [small] step forward towards solving the problem.

- It demonstrates that something useful *can* be done on this model, shattering a little the "good old" conviction that the sequential model is the best we can have.

- It does not end by giving the 397-th algorithm for parallel matrix multiplication, while still not solving the general problem.

There are some further reasons why I choose the systolic model and this particular area of applications, but explaining this already becomes "scientific", so please turn the page to see how the real story begins, and

### enjoy!

### 1.2 Object of the thesis

The title "Systolic multiprecision arithmetic" indicates

the problem we want to solve,

the domain of the problem,

and the *method*.

The context of our approach is symbolic (or algebraic) computation.

The problem is arithmetic, that is we want to efficiently perform operations like addition, multiplication, division, GCD computation.

The domain is that of **long integers**, that is very big integer numbers which can only be represented using several words (e.g. of 32 bits) in a conventional computer. We are interested in the range from 1 up to 100 words, because this is what occurs in typical algebraic computations. For the same reasons, we are looking for algorithms which perform well on operands of *various* sizes, which is different, for instance, from what is needed in cryptography. The domain also contains **long rationals**, that is, rational numbers which are represented by pairs of long integers. Because rational operations are sequences of integral operations, one has to find integral algorithms which perform well *together*. This is particularly interesting in the case of systolic algorithms, because if partial results (digits) can be pipelined between the different stages of computation, then these stages can overlap in time, leading to a significant increase of performance.

As a "side effect", sometimes algorithms for operations with **polynomials** are developed, because they are similar to the algorithms for long integers, and also because they are the main "users" of integral and rational algorithms.

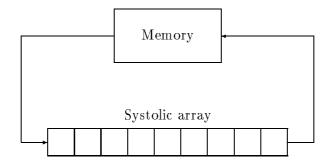

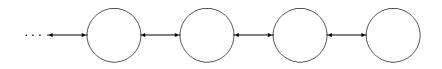

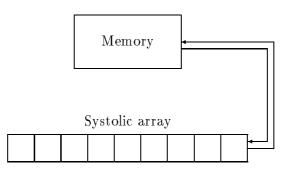

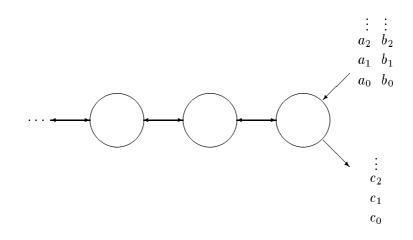

The *method* is **systolic parallelization**. The term systolic was introduced by [Kung and Leiserson, 1978] (see also [Kung and Leiserson, 1980, Kung, 1982]) and designates a parallel computation in which the data is "systolically" pumped from the memory through an array of processors and back again (see Fig. 1.1), exactly like the blood is pumped by the heart through the circulatory system.

The array could be also two- or three-dimensional, and the flow of information could be more intricate (different directions for different operands). Section 3.4 contains a guide to the literature on systolic computing.

In fact, this model can be seen as a practical application of the *cellular* automata theory, which was introduced by [von Neumann, 1951] (see also [von Neumann, 1966]). A cellular automaton is a regular network (we will

Figure 1.1: A systolic system

only consider linear arrays) of identical finite state machines (FSM). Each FSM evolution step depends on its own state as well as of the states of a finite number of neighbors (usually only the closest). More details on this model are presented in section 3.3.

One notes that the model is, in fact, quite restrictive. This is a disadvantage when designing algorithms for it, and a big disadvantage when trying to design parallelizing compilers for it (although some successful research has been going on – see e. g. [Dadda and Wah, 1993]). However, these restrictions have the advantages:

- the model has efficient practical implementations (SIMD, hardware);

- it is easy to solve problems like synchronization, deadlock elimination, routing, which are difficult on less restrictive models.

Consequently, if a good systolic algorithm is found, then it will be quite robust and most likely it will have a very efficient implementation.

Algebraic computations constitute the context of our approach (see also fig. 1.2). In the sequel we provide short description of the symbolic computation field and a rationale for our approach.

The need for *exact computations* is becoming more and more acute both in theoretical Mathematics and Computer Science and in industrial applications of these fields. Typical applications of symbolic computation are *Gröbner bases* [Buchberger, 1985a] (which is used, for instance, in solving systems of polynomial equations) and *quantifier elimination* [Collins, 1975] (which is used, for instance, in robot kinematics). Recent years have witnessed a continuous increase of the interest in this field, both from theorists

17

and practitioners (see e.g. [POSSO, 1992, Wang, 1992, Bronstein, 1993, Cohen, 1991, Cohen and van Gastel, 1992, H. F. Mattson, 1991, Cohen *et al.*, 1993]). A large collection of advanced computer algebra algorithms has already been created, which practically covers all the necessities (see e.g. [Buchberger *et al.*, 1982, Davenport *et al.*, 1988, Akritas, 1989]). Most of these algorithms are implemented in computer algebra systems available on all popular computers (Mathematica, Maple, Reduce, Axiom, Derive, etc.). However, the day-to-day use of these algorithms for actual problems occurring in scientific research and design has a major draw-back: the computing time spent in solving almost any non-trivial problem is so long, that in many cases the use of computer algebra systems is impractical. Therefore, any significant speed-up of computer algebra systems will not only result in an increasing user-commodity, but also in a significant enlargement of the area of tractable problems.

The use of coprocessors for solving basic and intensive computational tasks (as 32- or 64-bit integer arithmetic, floating-point arithmetic, graphics display, etc.) is largely spread in computing technology. Perhaps the most relevant example is floating-point arithmetic, which was once programmed/microprogrammed, then implemented in coprocessors and today it is embedded in the standard CPU of most modern computers. This evolution is due to the fact that, in recent decades, the most expensive practical computation tasks were of numerical nature.

When approaching computational problems which require arbitrary precision arithmetic, the natural question arises: Why not have specialized coprocessors for this kind of arithmetic? Certainly the frustration of the users of current computer algebra systems is at least partially due to the absence of such devices from their computers. What would be the performance of a contemporary numerical system if the floating-point operations were implemented in software?

The possibility of using special hardware for expensive algebraic computations has been already stated in [Davenport and Robert, 1985]:

In computer algebra systems (such as REDUCE and MACSYMA), the expressions manipulated are large and complicated, for example rational functions in several variables, and hence the algorithms suffer, in general, from a relative slowness (even when they are implemented on the most powerful computers).

Could one hope to increase the capacity or speed (or both) of these systems by implementing certain basic functions in hardware? We

#### 1.3. OVERVIEW

are not talking here about completely re-writing a computer algebra system, truly a major task, but adding certain specialized processors to increase the speed of critical algorithms. The progress of VLSI technology means that such implementations are **now** possible.

Also, in the authoritative overview report [Boyle and Caviness, 1990], page 58:

If custom chip design and manufacture become as easy as making photographic copies, special chips for important kernel components of symbolic computation may be justified.