Generation and Verification of Systolic Algorithms

> Laura Ruff Babes-Bolyai University Cluj laura@cs.ubbcluj.ro

> > March 22, 2007

# Contents

| <b>1</b> | Intr | oduction 7                                                                                                   |

|----------|------|--------------------------------------------------------------------------------------------------------------|

|          | 1.1  | Overview                                                                                                     |

|          | 1.2  | Acknowledgements                                                                                             |

| <b>2</b> | Sur  | ey 11                                                                                                        |

|          | 2.1  | Design Methodologies                                                                                         |

|          | 2.2  | Partitioning                                                                                                 |

|          | 2.3  | Verification of Systolic Arrays                                                                              |

|          |      | 2.3.1 General Aspects Concerning Formal Verification<br>Methods                                              |

|          |      | 2.3.2 Classification of the Formal Frameworks Used 22                                                        |

|          | 2.4  | Synthesis and Verification – Conclusions                                                                     |

|          | 2.4  | Synthesis and vermication – Conclusions $\ldots \ldots \ldots \ldots \ldots 25$                              |

| 3        | The  | Space-Time Transformation Methodology 26                                                                     |

|          | 3.1  | Introduction $\ldots \ldots 27$ |

|          | 3.2  | Timing Function                                                                                              |

|          |      | 3.2.1 Finding an Adequate Affine Timing Function 30                                                          |

|          | 3.3  | Allocation Function                                                                                          |

|          |      | 3.3.1 Obtaining an Adequate Allocation Function 33                                                           |

|          | 3.4  | Performing the Time-Space Transformation                                                                     |

|          | 3.5  | Polynomial Multiplication - Case Study                                                                       |

|          |      | 3.5.1 Uniformisation of the Recurrence Equation                                                              |

|          |      | 3.5.2 Finding an Adequate Timing Function                                                                    |

|          |      | 3.5.3 Possible Allocation Functions                                                                          |

|          |      | 3.5.4 Mappings to Different Systolic Arrays 40                                                               |

|          |      | 3.5.5 Other Solutions to the Problem                                                                         |

| 4        | Ma   | ping Systolic Arrays onto Fixed Size Architectures 47                                                        |

| т        | 4.1  | Introduction                                                                                                 |

|          | 4.2  | Steps of the Design Algorithm                                                                                |

|          | 4.3  | The Problem of Sequences Comparison - Case Study 54                                                          |

|   |     | 4.3.1          | Generating the Systolic Solutions for the<br>Sequences Alignment Problem                                                                |

|---|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| 5 | Fun | ctional        | l-Based Systolic Array Design 62                                                                                                        |

| 0 | 5.1 |                | $\begin{array}{c} \text{uction} \\ \dots \\ $                   |

|   | 0.1 | 5.1.1          | Functional View of Systolic Arrays   63                                                                                                 |

|   | 5.2 |                | Punctional View of Systeme Arrays    5      1 Background    65                                                                          |

|   | 0.2 | 5.2.1          | Scalars and Lists                                                                                                                       |

|   |     | 5.2.1<br>5.2.2 | Scalars and Lists                                                                                                                       |

|   |     | 5.2.2          | Properties of Online Transitive Functions                                                                                               |

|   |     | 5.2.5<br>5.2.4 | -                                                                                                                                       |

|   |     | 5.2.4<br>5.2.5 | 0                                                                                                                                       |

|   | 5.0 |                | 0                                                                                                                                       |

|   | 5.3 | v              | ic Processors                                                                                                                           |

|   |     | 5.3.1          | Systolic Processor without Internal State                                                                                               |

|   |     | 5.3.2          | Systolic Processor with Internal State                                                                                                  |

|   |     | 5.3.3          | Systolic Processor with Delay                                                                                                           |

|   |     | 5.3.4          | Auto-configurable Systolic Processor                                                                                                    |

|   | ~ 4 | TT · 1·        | $(\text{with Delay}) \dots \dots$ |

|   | 5.4 |                | ectional Arrays                                                                                                                         |

|   |     | 5.4.1          | Unidirectional Array with                                                                                                               |

|   |     | 540            | Input "Pass-Through"                                                                                                                    |

|   |     | 5.4.2          | Unidirectional Arrays with Delayed Input                                                                                                |

|   |     | 5.4.3          | Unidirectional Arrays with Delayed Output and Input                                                                                     |

|   |     | F 4 4          | "Pass-Through" $\dots \dots \dots$      |

|   |     | 5.4.4          | Unidirectional Pass–Through Array                                                                                                       |

|   |     | 5.4.5          | Unidirectional Array for GCD Computation – Case                                                                                         |

|   | ~ ~ | D' I'          | Study                                                                                                                                   |

|   | 5.5 |                | ctional Arrays                                                                                                                          |

|   |     | 5.5.1          | Bidirectional Array with One Directional                                                                                                |

|   |     | <b></b>        | "Pass-Through" Input                                                                                                                    |

|   |     | 5.5.2          | Bidirectional Array with Internal State                                                                                                 |

|   |     | 5.5.3          | Bidirectional Array with Two Directional                                                                                                |

|   |     |                | "Pass-Through" Input                                                                                                                    |

|   | - 0 | 5.5.4          | $Transformations \dots \dots$     |

|   | 5.6 |                | e Systolic Arrays                                                                                                                       |

|   |     | 5.6.1          | Online "Pass-Through" Arrays without Internal State . 137                                                                               |

|   |     | 5.6.2          | Arrays with Delayed Input "Pass-Through" 139                                                                                            |

|   |     | 5.6.3          | Synthesis Method for Arrays with Delayed Input                                                                                          |

|   |     | <b>.</b>       | "Pass-Through"                                                                                                                          |

|   |     | 5.6.4          | Functional-Based Synthesis of Systolic                                                                                                  |

|   |     |                | Online Multipliers - Two Case Studies                                                                                                   |

| CONTENTS      | 3   |

|---------------|-----|

| 6 Conclusions | 151 |

| References    | 152 |

# List of Figures

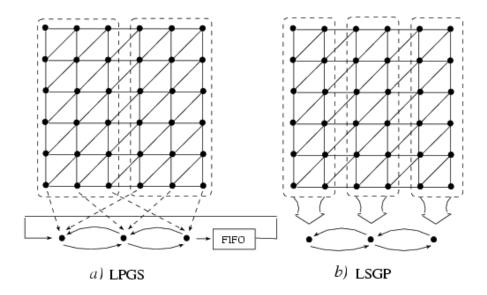

| 2.1 | LPGS and LSGP method [CK98].                                                                                                                                                                      | 18 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

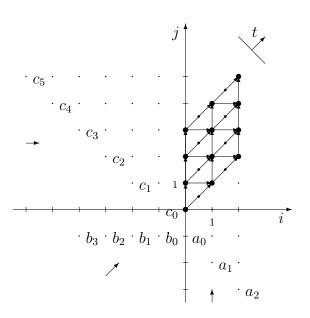

| 3.1 | Dependence Graph for Polynomial Multiplication $n = 3, m = 4$                                                                                                                                     | 43 |

| 3.2 | Systolic array for polynomial multiplication (the allocation                                                                                                                                      |    |

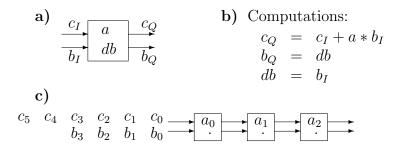

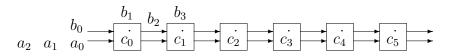

|     | function $p(i, j) = j - i$ was used)                                                                                                                                                              | 44 |

| 3.3 | Unidirectional systolic array for polynomial multiplication (the allocation function $p(i, j) = i$ was used for the projection) a) structure of a PE, b) transition function, c) structure of the |    |

|     | array and placement of the input values                                                                                                                                                           | 45 |

| 3.4 | Systolic array for polynomial multiplication (the allocation                                                                                                                                      |    |

|     | function $p(i,j) = j$ was used)                                                                                                                                                                   | 45 |

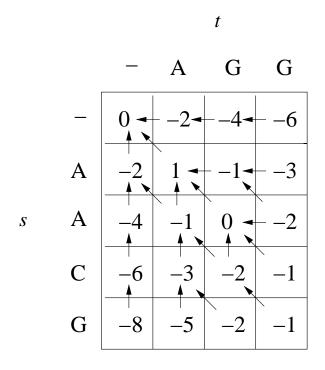

| 4.1 | Matrix A for scoring alignments of $s = AACG$ and $t = AGG$ .                                                                                                                                     | 55 |

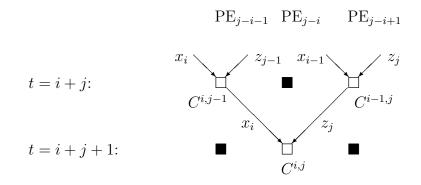

| 4.2 | Bidimensional systolic array for sequences alignment                                                                                                                                              | 57 |

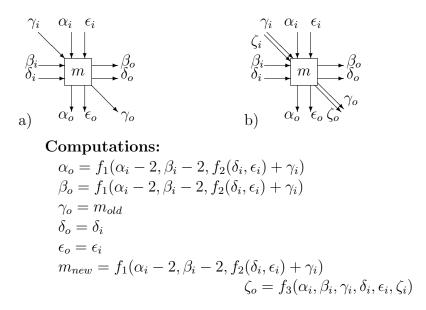

| 4.3 | Bidimensional systolic structure for the problem of sequences                                                                                                                                     |    |

|     | alignment. Computations of a PE                                                                                                                                                                   | 59 |

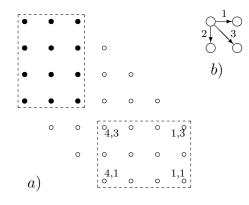

| 4.4 | Getting the result for the sequences alignment problem                                                                                                                                            | 60 |

| 4.5 | Linear systolic array for sequences alignment                                                                                                                                                     | 60 |

| 4.6 | Computations of a PE in the linear array for sequences com-                                                                                                                                       |    |

|     | parison                                                                                                                                                                                           | 61 |

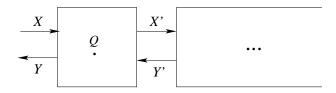

| 5.1 | Informal view of a linear systolic array                                                                                                                                                          | 63 |

| 5.2 | Systolic processor without internal state                                                                                                                                                         | 77 |

| 5.3 | Systolic processor with internal state register                                                                                                                                                   | 79 |

| 5.4 | An alternative view of the systolic processor with internal state                                                                                                                                 |    |

|     | register                                                                                                                                                                                          | 80 |

| 5.5 | Systolic processor with $k$ -delay                                                                                                                                                                | 81 |

| 5.6 | Systolic processor that computes $F[x_0, x_1, \ldots, x_{k-1}, T_k[X]]$                                                                                                                           | 84 |

| 5.7 | Auto-configurable systolic processor (with $k - 1$ -delay)                                                                                                                                        | 85 |

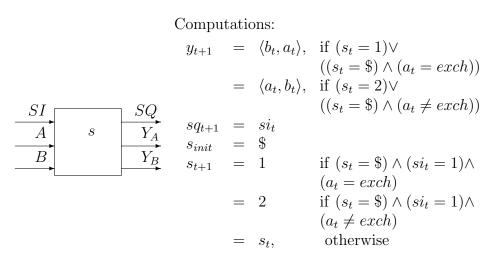

| 5.8 | Auto-configurable systolic PE for input-exchange                                                                                                                                                  | 87 |

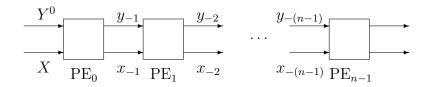

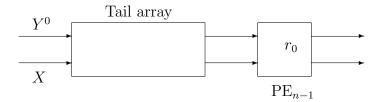

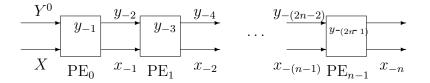

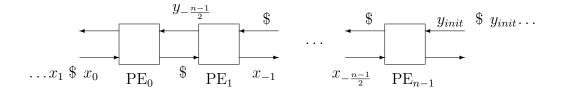

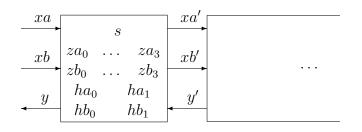

| 5.9 | Unidirectional array                                                                                                                                                                              | 89 |

| 5.10 | Unidirectional array with input "pass-through". Computa-                             |

|------|--------------------------------------------------------------------------------------|

|      | tions of a PE                                                                        |

| 5.11 | An alternative for the computation performed by an array characterised by $(5.23)$   |

| 5.12 | Functional view of a unidirectional array with internal state                        |

|      | register                                                                             |

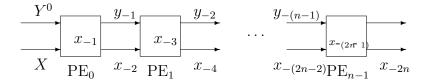

| 5.13 | Computation of a PE in an array with delayed input 98                                |

| 5.14 | Initial state of the array with delayed input                                        |

| 5.15 | Computation of a PE in an array with delayed output 104                              |

|      | Initialization of the array with delayed output                                      |

| 5.17 | Unidirectional Pass-Through array                                                    |

| 5.18 | PE for the problem of GCD computation                                                |

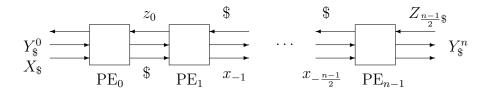

| 5.19 | Bidirectional array with one "pass-through" input. Initial state.117                 |

| 5.20 | Computation of a PE in a bidirectional array with one input                          |

|      | "pass-through"                                                                       |

| 5.21 | Bidirectional array with sparse input $(n \text{ is odd})$ . Initial state. 120      |

| 5.22 | Computation of a PE in a bidirectional array with one input                          |

|      | "pass-through" and constant internal state variables 121                             |

| 5.23 | Computation of a PE in a bidirectional array with one input                          |

|      | "pass-through" and variable internal state registers $\ . \ . \ . \ . \ 122$         |

| 5.24 | Computations of a PE in a bidirectional array with constant                          |

|      | and variable internal state registers, which can compute two                         |

|      | problems of the form $(5.50)$ - $(5.51)$                                             |

| 5.25 | Computation of a PE in a bidirectional array with two direc-                         |

|      | tional input "pass-through"                                                          |

| 5.26 | Bidirectional array with two directional sparse input. Initial                       |

|      | state ( $n$ is odd)                                                                  |

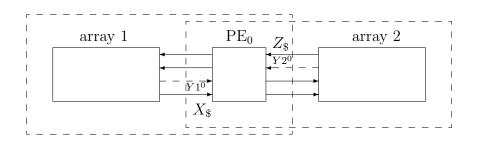

|      | Mirrored array                                                                       |

| 5.28 | Bidirectional array with bidirectional input and list of results.                    |

|      | Data-flow                                                                            |

| 5.29 | Data-flow. Fragment                                                                  |

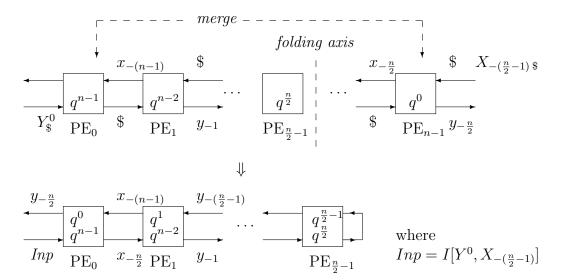

| 5.30 | Bidirectional "folded" array                                                         |

|      | Computation of a PE in a bidirectional "folded" array. $\dots$ 132                   |

| 5.32 | Computation of a PE in a bidirectional "folded" array. A                             |

|      | different view. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $134$ |

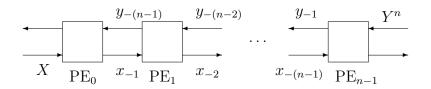

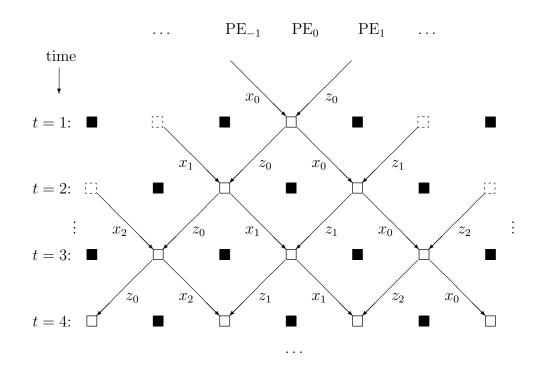

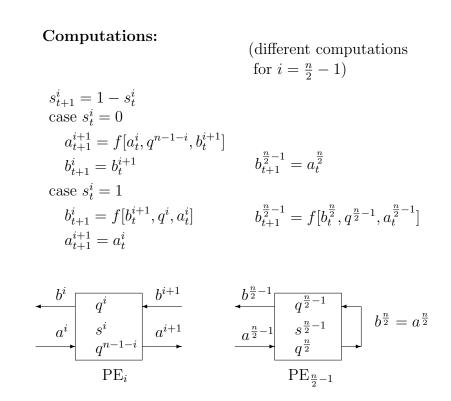

|      | Informal view of an online systolic array                                            |

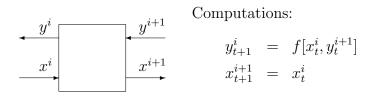

|      | Computations of a PE                                                                 |

|      | Initialization of the array                                                          |

| 5.36 | PE which performs the same computation as the array of Fig.                          |

|      | $5.35  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $              |

| 5.37 | Data flow in an array with input pass-through delayed by 2 141                       |

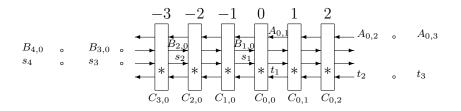

| 5.38 Online systolic array for polynomial multiplic | cation 147 |

|-----------------------------------------------------|------------|

|-----------------------------------------------------|------------|

## Chapter 1

## Introduction

... to be written later.

Some ideas to write about:

• thinking sequentially vs. parallel programming

Obvious advantages of parallel programming (speed, efficiency) **but** much more simple to write a sequential program.

- $\rightarrow$  **parallelisation** of sequential programs

- the systolic architecture

Systolic architectures are considered to be a very suitable means of implementing parallel algorithms in several areas, like linear algebra, signal processing, pattern matching, dynamic programming, etc. [Pet93]. The term *systolic* was fist introduced by Kung and Leiserson [KL78] (see also [KL80],[Kun82]), designating the parallel computation where the data is systematically "pumped" from the external memory through an array of processors, just like the human blood is pumped by the heart through the vascular system.

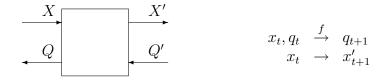

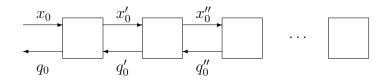

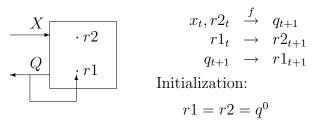

Systolic arrays combine pipelining and multiprocessing techniques, and are composed of a number of processing elements (**PE**), connected together by a *regular interconnection*. Each PE is performing - usually the same and very simple - computations on its input data and local memory variables, it stores data and is communicating with the neighbouring PE-s. The functioning of the PE-s is synchronised by a global clock, that results in a *regular data flow* through the system.

The systolic model suits very good for construction of high performance special purpose computer devices.

. . .

## 1.1 Overview

$\dots$  To be written later (at the moment is just copy-paste from the beginning of the chapters)

Chapter 2 (Survey): In this chapter we provide a short survey about the state of the research done in the field of automatic generation and verification of systolic arrays, used as starting point to our research. We first present the systolic array design methods available in the literature and sum up the main ideas used. We also compare them in order to find out the advantages and weak points of the most frequently used techniques.

Concerning the available formal verification methods, they are classified according to several comparison principles and the formal framework used.

Finally we summarise the main characteristics that we find the most important with respect to our research.

Chapter 3 The Space-Time Transformation Methodology : The *space-time transformation method* is the most commonly used design technique, more exactly it is the common name for the main ideas used in several design methods. All of these techniques are based on the concept of transformations applied to the index space representing the computations. The purpose of the transformations is to determine *where* and *when* the computations will be performed. This is the reason for the term "space-time" in the name of the method.

In this chapter we give a more detailed description of this particular design technique for the sake of a more precise comparison with our novel method presented in Chap. 5.

An interesting case study is presented at the and of the chapter, that will be revisited in Sect. 5.6.4, thus it can reveal the advantages and drawbacks of the two methods. The design of the case study was actually inspired by the online array generated with our functional-based method.

Chapter 4 Mapping Systolic Arrays onto Fixed Size Architectures:

Various attempts have been made to overcome the drawbacks of the spacetime transformation method.

We have chosen to present in this chapter an alternative method, that starts from an input of the same form as in the case of the space-time transformation methodology (recurrence equations), but the scheduling of the computations is obtained in a much simpler way.

This method is based on the ideas presented in [KRS95], [KRS96] that simplify the tedious task of finding an adequate timing function. The computations are represented by the nodes of a directed graph and the time function is given by the level of the nodes in the modified dependence graph after some empty nodes were introduces according to an algorithm based on rewrite rules, presented in [KRS94].

However, the price for the simplicity is that the size of the problem hs to be fixed in advance, thus the method does not work for parametrised problems.

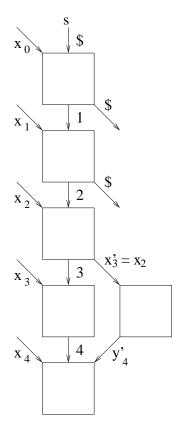

Again, the method is exemplified with a significative case study: a linear systolic array is generated for the problem of sequences alignment.

Chapter 5 Functional-Based Systolic Array Design:

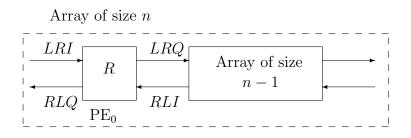

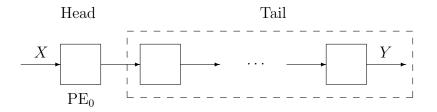

We introduce a *functional view* (or inductive view) of systolic arrays: a systolic array is composed of a *head processor* and an identical *tail array* of a smaller size. By exploiting the similarity between the inductive structure of a systolic array and the inductive decomposition of the argument by a functional program, it is possible to develop an elegant and efficient method for the automatic synthesis of systolic arrays.

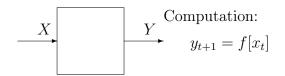

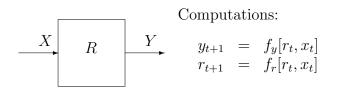

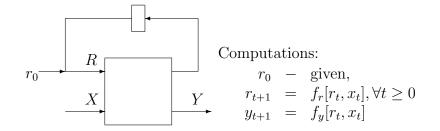

After a detailed presentation of the formal background used, we study the functioning of different systolic array-types.

By formal analysis, the structure of the functions which can be realised by arrays having certain properties is identified. Then, by equational rewriting, the expression of the list function which must be realised is transformed into an expression having the required structure. The resulting expression reveals the scalar function which must be implemented by each individual processor.

The utility and efficiency of the design method is demonstrated through examples and representative case studies.

Chapter 6 Conclusions and future work are summarised.

## 1.2 Acknowledgements

• • •

# Chapter 2

## Survey

In this chapter we provide a short survey about the state of the research done in the field of automatic generation and verification of systolic arrays, used as starting point for our research. We present at first the systolic array design methods available in the literature and sum up the main ideas used. We also compare them in order to find out the advantages and weak points of the most frequently used techniques.

Concerning the available formal verification methods, they are classified according to several comparison principles and the formal framework used.

Finally we summarise the main characteristics, that we find the most important with respect to our research.

## 2.1 Design Methodologies

The first examples of systolic arrays that appeared in the early eighties were designed intuitively, in an "ad-hoc" manner, requiring a great amount of creativity and inspiration of its inventors. Many researchers were fascinated by the simple and regular structure of systolic arrays, able to perform complex computations on a great amount of data in a very efficient way. Later on they proposed several systematic design methodologies to overcome the limitations of heuristics and designer intuition and to provide a formal framework for mapping algorithms to systolic architectures.

In this section we present a short survey about the research done in this field, highlighting the most important characteristics of the distinct design methods. We also point out the advantages and disadvantages of the several methods.

Among the first systematic design methodologies two seemingly distinct methods, called **data dependency method** and **parameter method** were proposed.

The essence of the *data dependency method* is the representation of the dependency structure of an algorithm in concise, matrix form. The technique for mapping algorithms into systolic arrays is based on the mathematical transformations of index sets and the so called *data dependence vectors*.

This method has been extensively studied by Fortes, Wah and Moldovan [Mol83], [MF86], [FW87], S.Y. Kung [Kun87] and others. The procedure based on this method and presented in [Mol83] was also implemented at the University of Southern California in a software package called ADVIS (automatic design of VLSI<sup>1</sup> systems).

A procedure for the derivation of optimal systolic design was first developed in the *parameter method* [LW85]. This methodology presents the optimal mapping of algorithms that are represented as *linear recurrences* onto systolic arrays. Three sets of parameters are used to characterise systolic arrays:

- velocities of data flow

- data distribution

- periods of computation

The relationship between these parameters are represented as constraint equations that control the correctness of the design, thus the design is formulated as an optimization problem.

<sup>&</sup>lt;sup>1</sup>Very Large Scale of Integration

The two design methodologies, the parameter method and the data dependency method are compared by O'Keefe, Fortes and Wah [OFW91], describing the relationship between them. It is shown that the parameter method applies to a subclass of the algorithms that can be processed by the dependency method. Explicit mathematical relations are established between the parameters, equations and constraints of the two important methods for the design of systolic arrays.

Also remarkable is the research carried out at Irisa in this field ([Qui84], [Qui87], [QR90], [QD89], [MQRS90]) that led to the design of a declarative language for systolic array description called *ALPHA* (see [VMQ91], [WS94]) and the corresponding program transformation environment, called Alpha du centaur ([GQMS88], [DVQS91]). Later another programming environment, called *MMALPHA* was written in Mathematica and C for manipulating Alpha programs.

The mentioned works, same as others like that of Delosme and Ipsen [DI86], Nelis and Deprettere [ND88], Huang and Lengauer [HL87] contributed to the foundation respectively the evolution of a unifying approach to the design of VLSI algorithms usually referred to as the **space-time transfor-mation methodology**. In a certain way, all the proposed methods by the above mentioned researchers vary very little, differing slightly in the degree of formalism and the way to approach the problem. In the ultimate instance, they all use the concept of transformation of dependencies. A review of the main ideas involved in these systolic algorithm synthesis methods is presented by Song in [Son94].

The task is the transformation of a sequential algorithm, expressed in the form of up to three nested loops, or in the form of *uniform recurrence equations* (see [KMW76]), into a systolic algorithm applying a set of mathematical transformations on the *dependence vectors*.

The computations involved in an algorithm, as well as the dependences between computations, are transformed by a *time function* and a *space allocation function*.

- The *time function* maps each computation of the algorithm to a positive integer that represents the time at which the computation is executed.

- The *allocation function*, on the other hand, obtains the position of the processing element to perform the computation involved.

Such a space-time mapping must satisfy several constraints to be valid. Basically two conditions has to hold:

- if a statement depends on the result of another statement, it should be executed after the result itself is available,

- two statements allocated to the same processor should not be scheduled at the same instant of time

If we restrict ourselves to the case when the transformations applied are linear functions, it appears that the above conditions can be equivalently expressed as a linear programming problem, when one considers uniform recurrences. Linear transformations have proven to be very effective in order to design locally connected architectures such as systolic arrays. These are the main reasons why research in this domain has mainly focused on uniform recurrences, and linear transformations.

A more detailed presentation of the space-time transformation method is provided in **Chap. 3**.

In most cases, the initial specification is expressed as a recurrence equation. However, the majority of the above mentioned works have worked with uniform recurrence equations (URE), a subclass of linear recurrence equations (LRE).

The uniformisation problem, that is to say the problem of transforming linear recurrence equations into uniform recurrence equations is tackled by Quinton and Dongen in [QD89], Fortes and Moldovan [FM84] and others. Such a transformation is mandatory when the target architecture is locally connected, as for example, a systolic array.

A more general review about the various transformations that can be applied to a system of recurrence equations is presented by Lavenier, Quinton and Rajopadhye in [LQR99].

The main formal manipulation techniques of SREs are summarised and exemplified:

- Serialization of Reductions

- Alignment

- Localization

- Change of basis

Many algorithms were already parallelised using the efficient technique of time-space transformations. However, this methodology also has some drawbacks. The constraint, that a location in space is assigned to each index value from the very beginning causes that the data will be introduced in a regular order. This is well suited for the design of regular architectures, but it also can lead to the exclusion of other possible solutions of the problem. Time and space boundary conditions often constitute another problem in the design of systolic arrays. The problem should usually be specified in the form of *uniform recurrence* equations (URE). The class of problems that can be expressed in this form is restricted and expressing most problems using UREs is not always an easy task.

Various attempts have been made to overcome the drawbacks of the spacetime transformation method. A remarkable alternate approach represents the methods based on viewing systolic design as program design.

Gribomont and Dongen presents another methodology for the mapping of systolic arrays based on the concept of **generic systolic array** introduced and illustrated in [GD92].

This approach represents a program-oriented methodology, being more closed to the program design. The technique takes in account two points, namely that:

- the architecture is often chosen before the real beginning of the development

- the basic operations to be executed by the individual cells are partially known at the beginning

Thus the development starts from a *generic systolic array*, whose parameters have to be instantiated. A more detailed description of the method is given in [GD92].

As already mentioned, this method is more closed to the program design, thus cannot be fully automated. It still needs some creativity and intuition from the designer.

Another disadvantage of the space-time transformation method is that it heavily depends on finding an affine timing function. The problem with finding an affine timing function is that one needs to solve a system of linear recurrence equations, which is generally difficult, and also possible only for systems having certain properties. The method proposed by Kazerouni, Rajan and Shyamasundar in [KRS95], [KRS96] is not restricted to affine timing functions.

They propose a general method for mapping a system of linear recurrence equations (SLRE) onto specific systolic architectures. Their method generates solutions suitable for existing target architectures rather than designing new ones. This means that the design method becomes easier, one does not have to solve a system of linear equations, but the solution is of fixed size, no parameters are taken into consideration. The method essentially consist of mapping *normalised linear recurrence equations*, a subclass of linear recurrence equations, - which properly includes the class of uniform recurrence equations - onto a generic architecture called *basic systolic architecture* and then applying correctness preserving transformations to adopt this intermediate solution onto specific target architectures (also presented in [KRS94]).

For additional details one may also see the short survey about the systolic array design methods available in the literature [Sza02a],[Sza02b].

## 2.2 Partitioning

The synthesis method for systolic arrays based upon space and time transformations can be extended to generate systolic implementations on a fixed number of processors. The main idea of all these extensions is to merge many cells into a single processor, so as to compress the array. This step is called *partitioning*. Algorithm partitioning is essential when the size of the computational problem is larger than the size of the systolic array intended for that problem.

It can take two different forms:

- The locally parallel globally sequential (**LPGS**) form, presented by Moldovan in [MF86].

- The locally sequential globally parallel (**LSGP**) form, studied by Darte, Delosme [DD90], [Dar91], Bu, Deprettere and Dewilde [BDD90].

The LPGS approach means that the array is first partitioned into blocks, the size of which is the number of available processors (p), and then each block one after the other is computed. The different computation points in the current block are allocated and scheduled in the p processors, in accordance to the dependence constraints. This method requires small local memories, but a large external buffer is needed to store the data used by the next block. In the LSGP approach the array obtained by the mapping procedure is partitioned into p blocks of virtual processors, each block being allocated to one physical processor.

Of course, the different points allocated to the same processor have to be computed at different times in the array in such a way that they can be sequentially executed by the physical processor. This method permits to synthesise systolic arrays with a fixed number of cells and, as a particular case, permits to improve the efficiency of the cells in a systolic array obtained by the projection method.

The two methods are illustrated in Fig. 2.1.

- a) In the LPGS scheme, the block size is chosen to match the array size, i.e. one block can be mapped to one array. All nodes within one block are processed concurrently, i.e. locally parallel. One block after another block of node data is loaded into the array and processed in a sequential manner, i.e. globally sequential.

- b) In the LSGP scheme, one block is mapped to one processing element (PE). Each PE sequentially processes the nodes of the corresponding block. The number of blocks is equal to the number of PEs in the array.

Figure 2.1: LPGS and LSGP method [CK98].

In the LPGS method, a general rule is to select a (global) scheduling that respects the data dependencies.

As to the scheduling scheme for the LSGP, after processor allocation, an acceptable (that is sufficiently slow) schedule is chosen so that at any instant there is at most one active PE in each block.

Note that the LPGS design has the advantage that blocks can be executed one after another in a natural order. However, this simple ordering is valid only when there is no reverse data dependence for the chosen blocks.

A unified partitioning and scheduling scheme is proposed for LPGS and LSGP in [HH95]. The main contribution includes a unified partitioning model and a systematic two level scheduling scheme. The unified partitioning model can support LPGS and LSGP design in the same manner. The systematic two level scheduling scheme can specify the intra-processor schedule and interprocessor schedule independently. Thus, more interprocessor parallelism can be effectively explored. The design methodology presented in [CK98] also proposes such a unified approach to the partitioning problem.

## 2.3 Verification of Systolic Arrays

An overview about the formal verification methods used for validating systolic arrays is presented in this section.

The traditional way of validating hardware systems was simulating and testing. This method is limited not only because of its expensiveness, but it is also hard to achieve total fault coverage. For this reason formal verification methods are considered more and more often as an alternative approach to ensure the quality and correctness of hardware designs [KG99].

Also the formal hardware verification methods have their limitation and the most significant one is their complexity. Even so, the regularity of the systolic systems and the simplicity of the processors make automatic reasoning and analysis possible.

## 2.3.1 General Aspects Concerning Formal Verification Methods

Formal verification is like a mathematical proof. The correctness of the hardware system is determined regardless of its input values, by considering its function rather than its behaviour, and by verifying logical properties.

Generally, when a formal verification has to be performed, two descriptions of the problem are given: a *specification* of the system and an *implementation*. Implementation and specification are in fact representations of the circuit at different levels of abstraction.

• the *specification* of the system describes how we expect the output data of the system to be related to the input data.

• the *implementation* describes how the system is built (behaviour of PE-s and how they are connected to each other in the circuit).

The task of formal verification is to check – using rigorous mathematical reasoning (instead of an experimental approach) – whether the given implementation really meets all parts of its specification.

A survey about formal hardware verification in general can be found in [Gup91] or [KG99].

Hereinafter we describe some important aspects, comparison principles to be taken into consideration when talking about formal methods of hardware verification, specially systolic array verification.

The first step towards developing an automatic verification method is to find an adequate formal framework that should aim to be simple, complete, precise, coherent, automatable, efficient and reliable. There have been many proposals for specification of systolic systems. They differ in expressiveness, treatment of semantics, range of applicability, etc.

The specification and implementation models used are: *logic* [Gor87] - propositional logic, first-order predicate logic, higher-order logic, temporal logic, or *automata/language theory* [Mil91] - finite state automata, trace structure, process algebra. An important aspect is the degree of automation offered by a verification technique, i.e. is it enough to describe the specification and the implementation in a proper way or we have to provide additional information during the verification process.

In the literature we find techniques ranging from completely automated methods (e.g. [LB99]) to interactive theorem proving using logical calculi (where the user should employ tactics or suggest appropriate lemmas during the verification process, e.g. Boyer-Moore theorem prover system [Gri88], [BM79], HOL system (due to M. Gordon) [Gor87], NURPL proof development system (due to N. Constable) [DLT89].

Another possibility to compare verification methods is to consider the class of systolic arrays that can be verified with a method. The size of the class of problems that can be verified with a certain method is usually in inverse proportion to the complexity of the method. This means that completely automated verification methods usually can be applied to a restricted class of systolic algorithms, while methods, which can solve a more general class of algorithms often require "extra information" (e.g. help lemmas, induction hypotheses) to succeed in performing the proof.

A good communication between designers and implementers is also a requirement, therefore the *ease of use* of a method could be an advantage compared to very general and powerful methods, that are restricted mostly to verification experts.

Another question concerning verification methods is how it could be applied. That means, whether it only gives a certification that the given implementation of the array is correct in respect to the problem it should solve, or we can also learn more about the array when performing the verification task. In the literature one can find formal frameworks and methods that are suitable not only for verification purposes but also for the design of systolic arrays, simulation, fault diagnoses (see [DQ94], [LB99]).

A hardware module can be abstracted at various *architectural levels*. Some examples of abstraction levels could be:

- *behavioural modeling* (also referred to as functional or system-level) the hardware module is described using a high level language by its logical behaviour rather than its physical implementation

- register-transfer level where the register values are the basic operands

with combinational logic blocks between them based on standard logic elements (multiplexer, shifter, adder)

- gate-level – description is based on standard logic gates like and, or, xor, not, etc.

Verification can be performed on different levels of abstraction or even in the course of successive steps on different levels of abstraction in a top-down or bottom-up manner. The implementation at a certain level i becomes the specification of a more detailed level i - 1 and the specification at level i is the implementation of a more abstract level i + 1.

The notion of *abstraction* permits unnecessary detail to be hidden from the high-level model.

Melham [Mel88] describes four different *types of abstraction* widespread in hardware verification.

- Structural abstraction hides the details about the implementation's internal structure in the specification. The specification gives a 'black-box' view of the design, that describes only the system's behaviour observable from outside, without entering into details about the internal design.

- Behavioural abstraction suppresses details about what the component does under operating conditions that should never occur. Behavioural abstraction may also include "don't care" conditions.

- Data abstraction relates signals in the implementation to signals in the specification when they have different representations. Data abstraction requires a mapping that determines how the states or signals of the implementation are to be interpreted in the specification's semantic domain.

- Temporal abstraction relates time steps of the implementation to time steps of the specification.

Ling an Bayoumi [LB89] specifies also another type of abstraction, specific for systolic arrays:

Abstraction of Systolic features: Systolic arrays have some particular properties at the array level. These are synchrony, regularity, repeatability, modularity, spatial and temporal locality, pipelinability and parallel processing ability [Kun87].

Abstraction of systolic features means to use a formalism (eventually introduce a new one) that exploits these properties.

## 2.3.2 Classification of the Formal Frameworks Used

Research in the domain of the formal verification of systolic arrays uses ideas, frameworks and techniques from various research fields including first or higher-order predicate logics, temporal logics, fixed-point induction, automated theorem proving, automata-theoretic techniques, language containment, process algebra, etc.

According to [KG99] from a conceptual point of view there are two main approaches to the specification and to the corresponding verification of hardware, referred to as: *property verification* respectively *implementation verification*.

## **Property Verification**

This approach is concerned with specifying desired *properties* for the design. Formal verification in this case is generally concerned with properties of a temporal nature. That means, it applies to the characteristics of the system's behaviour on execution rather than to static attributes of the system.

Temporal logics [Eme90] are a unifying framework for expressing such properties. Temporal logic – is a generalisation of predicate logic to enclose the temporal domain for effective description of dynamic environments. It substantially advances traditional logic because it can capture time and dynamic behaviours - essential features in hardware descriptions - with concise clear notation. It avoids the introduction of explicit time functions and time variables. [LB99]

The verification task consists in showing that all of the system's possible behaviours satisfy the temporal properties of its specification.

In [LB89] Ling and Bayoumi introduces a novel formalism based on *inter*val temporal logic (ITL), developed for systolic array reasoning, called Systolic Temporal Arithmetic (STA). The advantages of the developed formalism are its ease of use (STA does not require users to find out any assertions or loop invariants for verifications), the fact that the STA exploits systolic array properties to produce notation and reasoning methods suitable for systolic arrays to make specifications and verifications more simple and effective.

### Implementation Verification

This second approach is based on specification in terms of a high-level model of the system. In this framework, verification requires reasoning about the relationship between the high-level model, also referred to as *specification* and a lower-level model, that is the *implementation*.

In order to be able to reason about the implementation and the specification, formal interpretation must be given for their description. There are three common approaches to this formalisation:

1. Specification of the system's behaviour in terms of functions and predicates of *standard first or higher-order predicate logic*.

Theorem proving systems based on first or higher-order logic have been used to verify systolic circuits: the Boyer-Moore theorem proving system, based on first order logic, used to mechanise the verification method presented by Purushothaman and Subrahmanyam [PS89]; higher order logic systems like HOL, described in [Gor87] or NURPL in [DLT89].

2. Description of the system behaviour by a *state transition system*, whose definition can be expressed in languages such as CSP<sup>2</sup>.

Here we mention that due to the regularity of the systolic arrays recursivity is very often used in the description of such systems. Recurrence equations, specially *uniform recurrence equations* are most suitable for this purpose.

Gribomont [Gri88] uses a small language derived from Hoare's CSP to describe the processing units of the systolic array. Chen [Che83] uses systems of recursive equations to describe systolic circuits.

3. Description in terms of infinite languages recognised by a finite state automata.

In the paper of Margaria [Mar96] the internal structure of the basic cell is specified as a Finite State Machine and implemented in hardware at the gate-level.

<sup>&</sup>lt;sup>2</sup>CSP– Communicating Sequential Processes, a language for describing patterns of interaction between processes, introduced by C. A. R. Hoare [Hoa85]

## Top-Down Synthesis – Button-Up Abstraction – Meet in the Middle Comparison

Another approach to systolic array verification is the combination of the proof process with that of synthesis. In [DQ94] an interesting verification method is presented, where the proof process is a combination of top-down synthesis and bottom-up abstraction until a common middle-point is reached (the idea was proposed by Hans Eveking[Eve87]). This method takes into consideration also the available architectural synthesis methods for systolic arrays.

The formal representation of both, the specification and the implementation of an array is given in ALPHA, a functional/equational language used for synthesis of regular synchronous architectures [DQ94].

A circuit can be represented in the ALPHA language at different levels of abstraction: structural description as well as functional or temporal abstraction level.

The verification is performed by doing program transformations based on the semantics of ALPHA. The proof process is semi-automatic in the sense that the designer has to select transformations whose application is automatic. The proof methodology deals with parametrised circuits.

- The *specification* of the array consists of the recurrence equations describing its operations.

- The *implementation* is the actual model of the array at register transfer level.

By *synthesis*, the recurrence equations are transformed in an explicit architecture.

By *abstraction*, the implementation is simplified by eliminating all initialization mechanisms, and some optimizations which were applied when designing the array. The implementation is abstracted up to the same representation level by means of induction.

The *verification* is completed by matching both descriptions.

## 2.4 Synthesis and Verification – Conclusions

We provided in the former section a short survey about the systolic array verification methods available in the literature, pointing out their main characteristics, and we also gave some principles of comparison of these methods.

Temporal logics, specially interval temporal logic (ITL) turns out to be a very concise and powerful framework to reason about systolic arrays. In this case we are talking about property verification, as the formal verification is concerned with properties of a temporal nature, i. e. the characteristics of the system's behaviour on execution.

Due to the regularity of systolic array structure, recursivity is frequently used in their formal description. Therefore fixed-point induction is a commonly used technique in systolic array verification, though it is not always simple to find the fix-point of a recursive system. Theorem proving systems, based on first or higher-order logic are also used to automatically perform the proof or at least a part of it, but beside the advantage of the computational power of such a system there is usually also a disadvantage, namely that additional information (in terms of lemmas) has to be given to the system in order to succeed. This makes their use rather difficult, available only for experts.

It is hard, actually impossible, to find a "perfect" verification method, suitable for a large set of problems, completely automatic and also easy to use, not only for experts. Yet, we would like to point out some characteristics, we find the most important in connection with our work. A very important aspect is the appropriate choice of the modeling language, preferable to be closer to the modeling practice of hardware designers. Another important feature that we would expect from a verification method is not only to certificate the correctness of a given hardware but also to make it possible to gain more information about its design.

Systolic array synthesis and verification are two research fields strongly related to each other. In this context, we find the idea of combining the synthesis and the verification process very useful.

## Chapter 3

# The Space-Time Transformation Methodology

The space-time transformation method is the most commonly used design technique, more exactly it is the common name for the main ideas used in several design methods. All of these techniques are based on the concept of transformations applied to the index space representing the computations. The purpose of the transformations is to determine where and when the computations will be performed. This is the reason for the term "spacetime" in the name of the method.

In this chapter we give a more detailed description of this particular design technique for the sake of a more precise comparison with our novel method presented in Chap. 5.

An interesting case study is presented at the and of the chapter, that will be revisited in Sect. 5.6.4, thus it can reveal the advantages and drawbacks of the two methods. The design of the case study was actually inspired by the online array generated with our functional-based method.

## **3.1** Introduction

The **space-time transformation methodology** is a unifying approach to the automatic design of systolic algorithms based on the concept of transformation of dependencies. In the sequel we will present the basic notions and commonly used ideas characteristic to this method, pointing out also the difficulties encountered.

A common way of describing an algorithm is that of using abstract specifications such as *recurrence equations*.

The design methods based on the space-time transformation use as starting point the representation of the sequential algorithm in terms of a system of Uniform Recurrence Equations (URE), a subset of Linear Recurrence Equations. The reason for using URE systems is that only such systems are suitable for being directly mapped onto systolic architectures, as they require local data and local interconnections between the processing elements.

In order to apply the method to a larger set of problems - e. g. Linear Recurrence Equations - the problem of uniformisation should be studied (also discussed in [QD89]).

## Definition 3.1. Uniform Recurrence Equation System

A system of uniform recurrence equations (SURE) is a collection of  $s \in N$  equations of the form (3.1) and input equations of the form (3.2):

$$V_i(z) = f_i(V_1(z - \theta_{i_1}), \dots, V_k(z - \theta_{i_k}))$$

(3.1)

$$V_i(z_i^j) = v_i^j, j \in \{1, ..., l_i\}$$

(3.2)

where

- $V_i : D \to R$ .  $V_i, i \in \{1, \ldots, s\}$  are variable names belonging to a finite set V. Each variable is indexed with an integral index, whose dimension, n (called the *index dimension*), is constant for a given SURE (in practice this is usually 2 or 3).

- $z \in D$ , where  $D \subseteq \mathbb{Z}^n$  is the domain of the SURE. (In the following we consider limited convex polyhedral domains. See [Wil93]).

- $v_i^j$  is a scalar constant (input),  $z_i^j \in D_{inp}$ , where  $D_{inp} \subseteq \mathbb{Z}^n$  is the domain of the inputs.

- $\theta_{i_1}, \ldots, \theta_{i_k}$  are vectors of  $Z^n$  and are called *dependence vectors* of the SURE.

- $V_i(z)$  does not appear on the right-hand side of the equation

-  $f_i: R^s \to R$

Note: We gave a simplified form for the equations of a SURE in (3.1), respectively (3.2). Generally a computation may consist of several cases. Also the domains associated to the several computations may be different. A more general form for the input equations would be the following:

$$V_{i}(z) = \begin{cases} f_{i,1}(\ldots) & , z \in D_{i,1} \\ \dots & \\ f_{i,c}(\ldots) & , z \in D_{i,c} \end{cases}$$

(3.3)

where  $D_{i,n} \cap D_{i,m} = \emptyset$  for  $n \neq m$ .  $D_i = \bigcup_{j=1,c} D_{i,j}$ . The domain D of the SURE is the convex hull of all  $D_i$  domains. In the same way, the input equations may also consist of more cases.

Unless it is uniform, a system of recurrence equations cannot be mapped directly on a systolic array. Indeed, if the dependence vectors are not constants, the PEs may have to communicate with an arbitrary large number of other PEs (also called *broadcasting*), and this is not desirable for a systolic array, where the PEs should only be connected with their neighbours.

#### **Definition 3.2.** (Dependence Vectors)

Let  $\Theta = \{\theta_0, \theta_1, \dots, \theta_l\}$  the set of vectors  $\theta_i$  of a *SURE* of the form (3.1)-(3.2). The  $\theta_i$  vectors are called *dependence vectors* of a system.

Consider points  $z, z' \in D$ . We say that z is dependent on z' by  $\theta_i$ , if  $\exists \theta_i \in \Theta$ , such that

$z = z' + \theta_i.$

Given a SURE of the form given in definition 3.1, we say that the variable instance  $V_i(z)$  depends on  $V_j(z')$  if there is an equation of the form (3.1), where  $V_i(z)$  appears on the lhs. of the equation and  $V_j(z')$  is on the rhs. We denote the dependence by  $V_i(z) \leftarrow V_j(z')$ .

The dependences can be represented by a directed graph called *dependence graph* of the SURE. It abstracts the dependency relations among the variables in the SURE.

#### Definition 3.3. (Dependence Graph - DG)

The dependence graph of a SURE is a directed graph G(V, E), (also denoted by  $(D, \Theta)$ ), where the set of nodes V = D, i.e. the nodes are points of D, and the set of advect  $E = (a + \Box 0, C, \Omega)$  are r(t + 0), i.e. if using dependent are r(t + 0).

the set of edges  $E = \{ \varepsilon_{zz'} | \exists \theta_i \in \Theta, z = z' + \theta_i \}$ , i.e. if z is dependent on z' by  $\theta_i$ , there exists an edge from node z' to node z.

Informally, a SURE (as well as the associated dependence graph) can be seen as a multidimensional systolic array, where the points of the domain D(respectively the nodes of the DG) are the PEs of the array and the communication channels are determined by the dependencies (the edges of the DG). In this context a transformation applied to the system that preserves the number of domain points and the dependencies leads to a computationally equivalent system. The goal of such a transformation is to obtain a system where one of the indices can be interpreted as the *time index* and the others as *space-indices*.

Linear (and affine) transformations are most commonly used because they preserve the dependencies between the computations. Moreover, if the transformation is *unimodular*<sup>1</sup>, then it has the advantage that it preserves the number of points in the domain, and in addition it admits an integral inverse. However it is not mandatory to use unimodular transformations.

In the following sections we show how an adequate timing function respectively allocation function can be found.

## 3.2 Timing Function

Given a URE system, we want to obtain a timing function t that schedules the computations associated to the points of domain D. For a given  $z \in D$ we assume that the computations  $V_i(z)$  are performed in parallel, and take a unit time.

A natural requirement is that in order to perform the computations of  $V_i(z)$ , its arguments should have been computed before. The time function t associates to each point  $z \in D$  the time instant when it is computed, such that the dependencies are respected. If such a function exists, then we say that the *SURE* is *computable*.

#### **Definition 3.4.** (Timing Function)

For each variable  $V_i$  of the SURE of the form given in definition 3.1, we call the timing function of the variable  $V_i$  the positive function  $t_{V_i} : D \to \mathcal{N}$ , that gives for any point z of the domain D the time instant when  $V_i(z)$  will be computed, such that for each dependence  $V_i(z) \leftarrow V_j(z')$  of an equation of the form (3.1) should hold:

$$t_{V_i}(z) > t_{V_i}(z')$$

.

<sup>&</sup>lt;sup>1</sup>A transformation x' = Ax is unimodular if the determinant of the matrix A satisfies  $det(A) = \pm 1$ .

For each variable  $V_i$  of the equations of the form (3.1) of a SURE, we are looking for an affine timing functions  $t_{V_i} : D \to \mathcal{N}$  having the same linear part:

$$t_{V_i}(z) = T * z + \delta_{V_i}$$

Note that T is an  $1 \times n$  vector  $T = (t_1, \ldots, t_n)$ . The fact that the timing function has the same linear part for each variable assures that after performing a transformation on the *SURE* according to the timing functions, the uniformity of the *SURE* will be preserved.

#### Constraints

The timing function has to satisfy the following two conditions:

1. (positivity constraint)  $\forall V$  variable of the  $SURE, \forall z \in D$ ,

$$t_V(z) \ge 0 \tag{3.4}$$

2. (dependency constraint) For each dependence  $V_i(z) \leftarrow V_j(z')$  of an equation of the form (3.1) should hold:

$$t_{V_i}(z) > t_{V_j}(z')$$

(3.5)

The first condition is a matter of convenience, since t is interpreted as time. The second condition makes scheduling of dependent computations possible.

We might also want to minimise the computation time of the system. This would mean to add the corresponding restriction on T, namely that the sum  $t_1 + \ldots + t_n + \sum_{V_i} \delta_{V_i}$  should be minimised.

## 3.2.1 Finding an Adequate Affine Timing Function

The previously mentioned constraints build a system of inequalities. Any of its solutions - if there exists any (that means, the system is computable) - gives an adequate timing function. The problem of the computability of a *SURE* in its full generality is undecidable [SQ93]. However there exists necessary and sufficient conditions for the restricted class of *affine timing functions*, which is of practical interest.

The theorem 3.1 of Quinton and Roberts gives a method to automatically determine, whether there exists an affine timing function for a parametrised system of equations. The method based on it is also referred to as vertex method. Its details are presented in [Qui87] and [QD89].

#### **Theorem 3.1.** (Quinton and Roberts [QR90])

For a given SURE, with dependence graph  $(D; \Theta)$  and set  $V_D$  of vertices of D, the parameters  $\lambda_0, \lambda_1, \ldots, \lambda_{n-1}$  and  $\gamma$  define a timing function t iff

- 1.  $\forall v_i \in V_D, \lambda^T v_i + \gamma \ge 0$  and

- 2.  $\forall \theta_i \in \Theta, \lambda^T \theta_i > 0$ , or  $\lambda^T \theta_i \ge 1$ .

See [QR90] for the proof.

Note that if z is dependent on z' by  $\theta_i$ , or  $z = z' + \theta_i$ , then

$$\lambda^T \theta_i = \lambda^T (z - z') = t(z) - t(z').$$

Thus  $\lambda^T \theta_i$  expresses the *delay* between the computation of z and the computation of z'. Theorem 3.1 requires this delay to be greater than 0 (at least 1).

Theorem 3.1. gives conditions for the obtainment of a time function. Another question is that of optimality of the time function. Several criteria for optimality can be adopted. Consider a *SURE* with dependence graph  $(D; \Theta)$ . One criterium is to minimise the delay between dependent computations according to a dependence  $\theta_k \in \Theta$ . Thus we want to minimise  $\lambda^T \theta_k$ , subject to

$$\lambda^T \theta_i \ge 1, \forall \theta_i \in \Theta.$$

An alternative method for the compression of the constraints into a finite set is the so called *Farkas method* [Fea92], that uses the following version of the Farkas Lemma:

## **Theorem 3.2.** (affine form of Farkas lemma)

Let *D* be a polyhedron defined by the inequalities  $A * z + b \ge 0$ , where *A* is a  $k \times n$  matrix. Then the affine form  $\phi$  is non negative on *D* if and only if there exist  $\lambda_0, \Lambda = (\lambda_1, \ldots, \lambda_k) \ge 0$  such that  $\phi = \Lambda(A \ b) + \lambda_0$ .

See [Sch86] for the proof.

A linear constraint can always be written in the form that a linear function is positive on a domain, thus one can make use of Theorem 3.2.

According to the method presented in [Fea92], the conditions (3.4) - (3.5) that a timing function t must satisfy can be replaced in the following way using Theorem 3.2:

#### • positivity constraint:

if a variable V is defined on the domain  $D_V = \{z | a_i z + b_i \geq 0, 1 \leq i \leq k\}$ , the timing function  $t_V(z) = T * z + \gamma_V$ ,  $(T = (\tau_1, \ldots, \tau_n))$  is positive on  $D_V$  iff  $\exists \lambda_0, \Lambda \geq 0$

$$\begin{cases} T * z + \gamma - \sum_{i=1}^{k} \lambda_i (a_i * z + b_i) - \lambda_0 = 0\\ \lambda_i \ge 0, \quad 0 \le i \le k \end{cases}$$

(3.6)

From 3.6 we have n + 1 equations:

$$\begin{cases} \tau_j - \sum_{i=1}^k \lambda_i * a_{ij} = 0 & 1 \le j \le n \\ \gamma - \sum_{i=1}^k \lambda_i * b_i - \lambda_0 = 0 & \\ \lambda_i \ge 0 & , 0 \le i \le k \end{cases}$$

(3.7)

#### • dependency constraint:

If a variable V(z) depends on W(z'), by  $\theta = z - z'$  on the domain  $D_{VW} = \{z | A * z + b \ge 0\}$ , where A is an  $k \times n$  matrix, then the timing functions  $t_V(z) = T_V + \gamma_V$  and  $t_W(z) = T_W + \gamma_W$  ( $T_V = (\tau_1^V, \ldots, \tau_n^V)$ ),  $T_W = (\tau_1^W, \ldots, \tau_n^W)$ ) respect the dependency constraints, that is  $t_V(z) - t_W(z') - \delta \ge 0$  ( $\delta$  is a delay between the computation of W and V) iff  $\exists \mu_0, (\mu_1, \ldots, \mu_k) \ge 0$

$$\begin{cases} T_V * z + \gamma_V - T_W * z' - \gamma_W - \delta - \sum_{i=1}^k \mu_i (a_i * z + b_i) - \mu_0 = 0\\ \mu_i \ge 0, \quad 0 \le i \le k \end{cases}$$

(3.8)

Again, from (3.8) we have n + 1 equations:

$$\begin{cases} \tau_{j}^{V} - \tau_{j}^{W} - \sum_{i=1}^{k} \mu_{i} * a_{ij} = 0 & 1 \le j \le n \\ \gamma_{V} - \gamma_{W} - \delta - T_{W} * \theta - \sum_{i=1}^{k} \mu_{i} * b_{i} - \mu_{0} = 0 & (3.9) \\ \mu_{i} \ge 0 & , 0 \le i \le k \end{cases}$$

#### • objective function constraints:

Using the Farkas method, one can find many schedules that satisfy the positivity and dependency constraints. This additional type of constraints depends on our choice related to the optimization of the problem from a certain point of view (this could be for example the minimization of the overall execution time).

## 3.3 Allocation Function

Given a suitable timing function, the next step is to find an adequate allocation function.

## **Definition 3.5.** (Allocation Function)

For each variable  $V_i$  of the *SURE* of the form given in definition 3.1, we call the *allocation function of the variable*  $V_i$  the function  $p_{V_i} : D \to D'$ , such that  $D' \subseteq Z^{n-1}$  and for any point  $z \in D$ ,  $p_{V_i}(z)$  is the index of the PE where the computation of  $V_i(z)$  will take place.

Given an affine timing function with the same linear part for every variable  $V_i$ , we are looking for an adequate allocation functions having the same property. That is  $\forall V_i$  of the equations of the form (3.1) of the *SURE* we should find an allocation function  $p_{V_i}: D \to D'$  of the form

$$p_{V_i}(z) = P * z + \gamma_{V_i},$$

where  $D' \subseteq \mathbb{Z}^{n-1}$ .

## 3.3.1 Obtaining an Adequate Allocation Function

We describe in this section how a set of constraints can be set up for the obtainment of suitable allocation function(s) for a given timing function.

## Constraints

The following set of constraints can be defined:

## General constraint:

In order to get an adequate allocation function for a given timing function, the condition that should hold can be intuitively expressed in the following way: two different computations performed at the same time-step should not be mapped onto the same PE. This means that the linear part P of the allocation function should not be parallel to the direction T corresponding to the timing function.

Formally:

$$P \neq c * T, \tag{3.10}$$

where  $c \in \mathcal{Z}$  is a constant.

## Weak conditions:

For every dependence  $V_i(z) \leftarrow V_j(z')$  of an equation of the form (3.1) such that  $V_i \neq V_j$ , the following condition should hold:

$$\|p_{V_i}(z) - p_{V_i}(z')\| \le t_{V_i}(z) - t_{V_i}(z') \tag{3.11}$$

(that is the value  $V_j(z')$  should be computed "close enough" to the place where  $V_i(z)$  will be computed, so that it can arrive from PE with index  $p_{V_i}(z')$  to PE with index  $p_{V_i}(z)$  in  $t_{V_i}(z) - t_{V_j}(z')$  time steps).

#### Strong conditions:

We define the data-flow direction for each variable  $V_i$ .

#### **Definition 3.6.** (Data-Flow Direction)

In the case of the variable  $V_i$ , if in the equation of the form (3.1) that computes  $V_i(z)$ , there is one and only one occurrence of variable  $V_i$  on the *rhs* of the equation, such that  $V_i(z)$  depends on  $V_i(z-\theta_{V_i})$ , then we obtain the *data*flow direction of variable  $V_i$ , denoted  $Dir_{V_i}$  by applying the linear time-space transformation (T, P) onto the dependence  $\theta_{V_i}$ :

$$Dir_{V_i} = (T * \theta_{V_i}, P * \theta_{V_i}),$$

where the component  $T * \theta_{V_i}$  indicates the "velocity" of  $V_i$  and the component  $P * \theta_{V_i}$  shows the "direction" along which  $V_i$  will be transmitted.

For each dependence  $V_i(z) \leftarrow V_j(z')$  of an equation of the form (3.1) such that  $V_i \neq V_j$ , the following should hold:

$$\|p_{V_i}(z) - p_{V_j}(z')\| = \left\lfloor \frac{t_{V_i}(z) - t_{V_j}(z')}{T * \theta_{V_j}} \right\rfloor P * \theta_{V_j}$$

(3.12)

## 3.4 Performing the Time-Space Transformation

Given the timing function  $t_{V_i}$  and the allocation function  $p_{V_i}$  for each variable of the *SURE*, we apply these functions onto the system, performing a so called "time-space transformation" (that means a transformation performed on the index space of the system). As a result we get an equivalent system in which the first index of the domain can be interpreted as the *time index* (representing the time instant when a certain computation takes place) and the other indices are the *space indices*, denoting the number of the PE where a certain computation takes place.

A computation  $V_i(z), z \in D$  will take place at the time instant  $t = t_{V_i}(z)$ at the PE with number  $p = p_{V_i}(z)$ . We denote the computation in the transformed *SURE* corresponding to  $V_i(z)$  with  $\overline{V_i}(t,p)$ . The time-space transformation corresponding to variable  $V_i$  is  $Tr_{V_i}: D \to \overline{D}$ , such that  $\forall z \in D, Tr_{V_i}(z) = (t_{V_i}(z), p_{V_i}(z)).$  There exists the inverse function  $Tr_{V_i}^{-1}: \overline{D} \to D$ , such that  $\forall (t,p) \in \overline{D}$ , the computation  $\overline{V_i}(t,p)$  of the transformed *SURE* corresponds to the computation  $V_i(Tr^{-1}(t,p))$  from the original system.

The time-space transformation is performed in the following way:

- In all equations of the form (3.1):

- we replace  $V_i(z)$  on the *lhs* of the equation with  $\overline{V_i}(t, p)$ , and

- for each dependence  $V_i(z) \leftarrow V_j(z-\theta)$ : we replace  $V_j(z-\theta)$  by  $\overline{V_j}(t_{V_j}(Tr_{V_i}^{-1}(t,p)-\theta), p_{V_j}(Tr_{V_i}^{-1}(t,p)-\theta))$ .

On the following scheme the arrows depict how the correspondencies between computations of the original, respectively the transformed SURE are found:

n.:

$$\overline{V_i}(t,p)$$

dep. on  $\overline{V_j}(t_{V_j}(Tr_{V_i}^{-1}(t,p)-\theta), p_{V_j}(Tr_{V_i}^{-1}(t,p)-\theta))$

$\downarrow$   $\uparrow$

o.:  $V_i(Tr_{V_i}^{-1}(t,p))$  dep. on  $V_j(Tr_{V_i}^{-1}(t,p)-\theta)$

where "o." stands for the original and "n." for the new dependency.

## 3.5 Polynomial Multiplication - Case Study

In this section we present a detailed case study which describes the design process of a systolic array for polynomial multiplication. The problem is a relatively simple one, however the array that we obtain is not trivial. The choice for this particular problem becomes even more interesting because it is revisited is Sect. 5.6.4 where an online array is generated with our functional– based method. Thus the problem presented reveals the differences, advantages and disadvantages of the two design methods.

#### Specification:

Let A and B two univariate polynomials of degree n-1 and m-1 respectively:

$$A = a_0 + a_1 * x + a_2 * x^2 + \ldots + a_{n-1} * x^{n-1}$$

$$B = b_0 + b_1 * x + b_2 * x^2 + \ldots + b_{m-1} * x^{m-1}$$

We denote the product of A and B with C (polynomial of degree n + m - 1),

$C = A * B = c_0 + c_1 * x + c_2 * x^2 + \ldots + c_{m+n-2} * x^{n+m-2},$

where

$$c_k = \sum_{i+j=k} a_i * b_j, \quad \forall k, \ 0 \le k \le m+n-2; 0 \le i \le n-1, 0 \le j \le m-1$$

(3.13)

We would prefer a recursive description of the coefficients of C rather than that given in equation (3.13). One possibility is to use the following notation (where  $A_i$  stands for  $a_i$  if  $0 \le i \le n-1$ , otherwise it is 0. Similarly  $B_j = b_j$  if  $0 \le j \le m-1$ , and 0 otherwise.):

$$A*B = \underbrace{A_0 * B_0}_{C_{0,0}} + \underbrace{(A_0 * B_1 + A_1 * B_0)}_{C_{0,1}} * x + \underbrace{(A_0 * B_2 + A_1 * B_1 + A_2 * B_0)}_{C_{0,2}} * x^2 + \underbrace{(A_0 * B_3 + A_1 * B_2 + A_2 * B_1 + A_3 * B_0)}_{C_{0,3}} * x^3 + \dots$$

Generally:  $\forall i, j: 0 \le i \le j; i+j \le m+n-2$

$$C_{i,j} = \begin{cases} A_i * B_i &, i = j \\ A_i * B_j + A_j * B_i &, j = i+1 \\ A_i * B_j + A_j * B_i + C_{i+1,j-1} &, j > i+1 \end{cases}$$

(3.14)

The result:  $c_k = C_{0,k}, \forall k, 0 \le k \le m + n - 2.$

## 3.5.1 Uniformisation of the Recurrence Equation

In equation (3.14)  $A_i$  is needed in the computation of  $C_{i,j}$  for all values of j,  $i \leq j \leq m + n - 2 - i$  this means a broadcast of  $A_i$  (to ...). Similarly  $A_j$ is needed in the computation of  $C_{i,j}$ ,  $\forall i, 0 \leq i \leq m + n - 2 - j$ . A common method to eliminate broadcast is to pipeline the given value through the nodes where it is needed (see [QD89]). Thus we replace  $A_i$  with a new variable  $A1_{i,i}$ , and pipeline it in the direction  $(i, j) \rightarrow (i, j + 1)$ .  $A_j$  will be replaced by the variable  $A2_{0,j}$  and pipelined through the direction  $(i, j) \rightarrow (i + 1, j)$ .  $B_i$  and  $B_j$  will be replaced in the same way with B1 and B2 respectively. We obtain the following uniform recurrence equation:

$$\forall i, j: \ 0 \le i \le j; \ i+j \le m+n-2$$

$$C_{i,j} = \begin{cases} A2_{i,j} * B2_{i,j} &, j = i \\ A1_{i,j} * B2_{i,j} + A2_{i,j} * B1_{i,j} &, j = i+1 \\ A1_{i,j} * B2_{i,j} + A2_{i,j} * B1_{i,j} + C_{i+1,j-1} &, j > i+1 \end{cases}$$

(3.15)

(3.16)

(3.17)

$$A1_{i,j} = \begin{cases} A_i & , j = i \\ A1_{i+1} & , j > i \end{cases}$$

(3.18)

$$\begin{pmatrix}

A1_{i,j-1} & , j > i & (3.19) \\